- 全部

- 默认排序

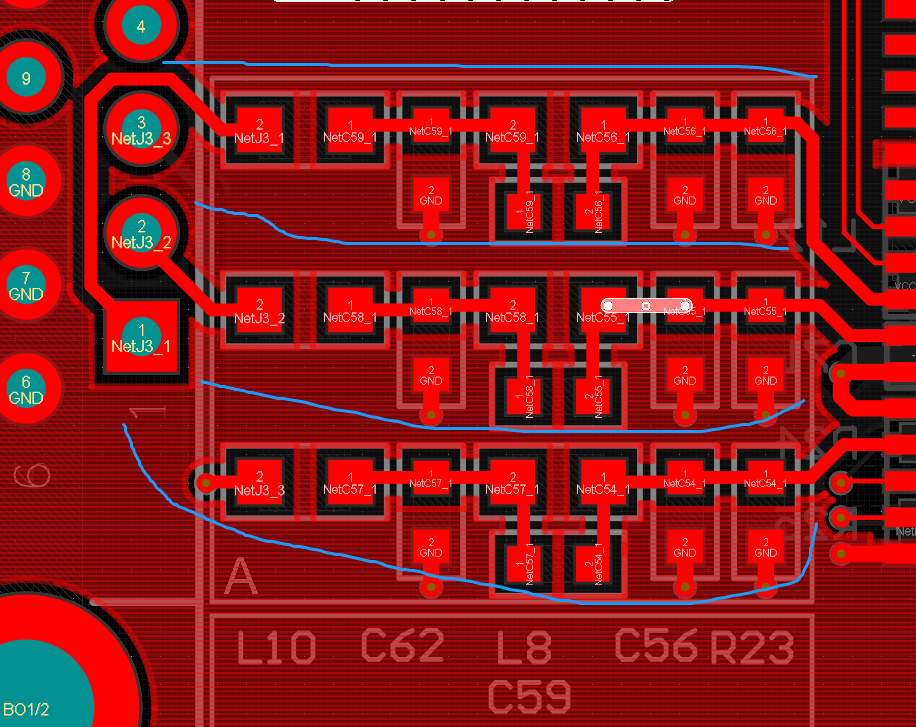

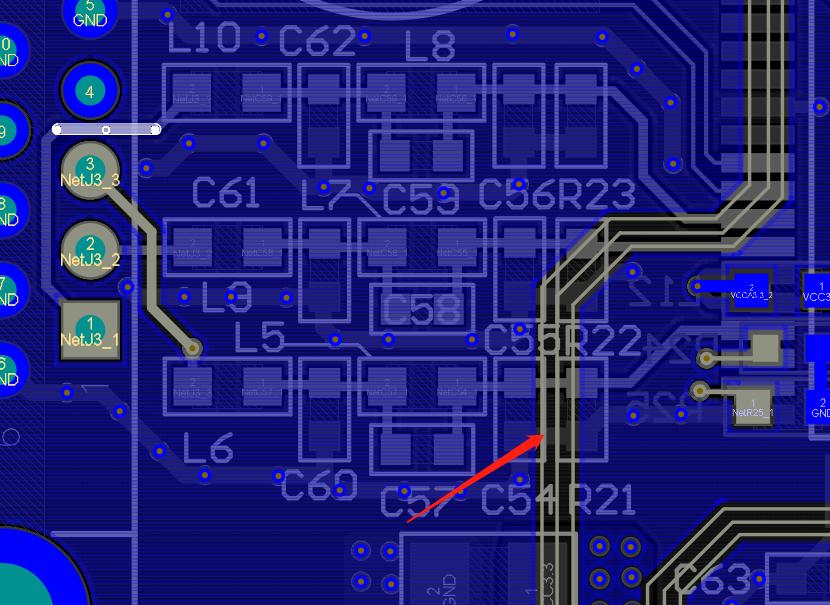

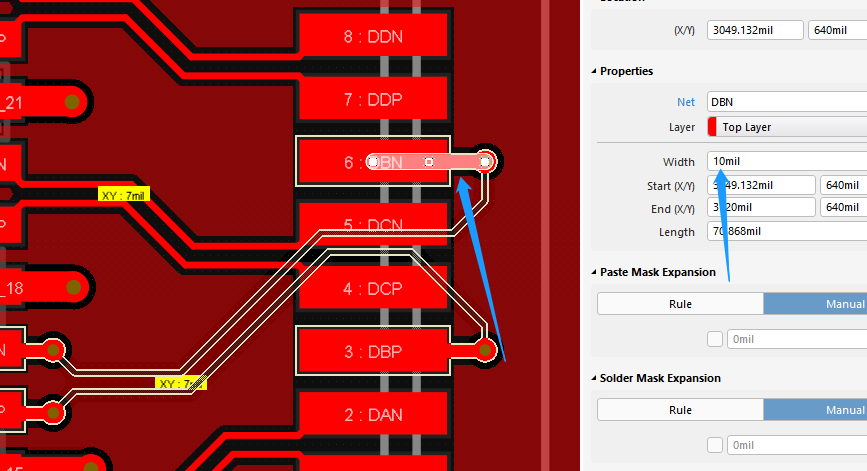

差分线对内等长凸起高度不能超过线距的两倍2.等长线之间尽量要满足3W规则,后期自己调整一下走线间距3.电源走线路径要尽量短,后期自己优化一下走线路径4.左右声道尽量单根包地5.差分走线要尽量耦合出线,后期自己调整一下地过孔6.注意天线部分挖

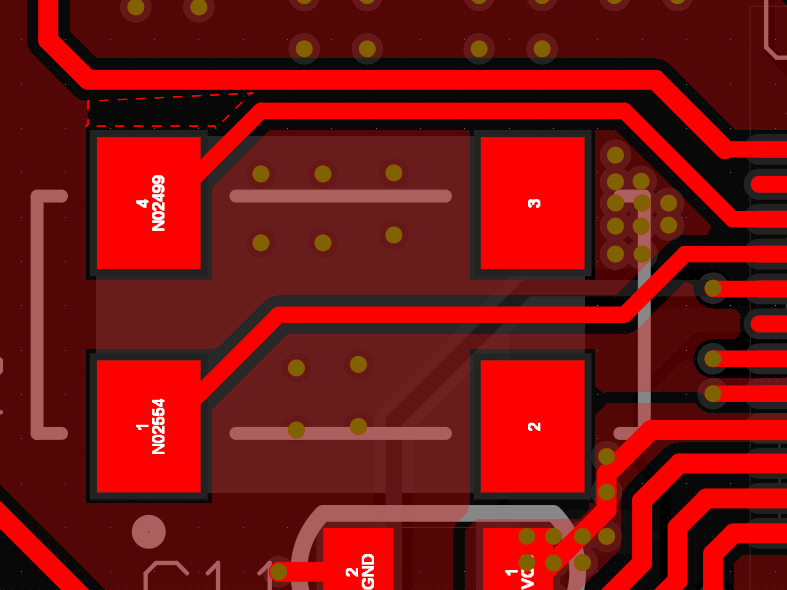

模拟信号单根包地处理,地线上多打地过孔2.跨接器件旁边尽量多打地过孔,间距最少1mm,有器件的地方可以不满足3.百兆网络差分对内等长误差5mil4.模拟信号需要加粗处理5.电感所在层的内部需要挖空处理6.反馈线需要加粗到10mil电源输入过

模拟信号下面不要走线其他信号线2.晶振走线内差分需要再优化一下3.跨接器件旁边尽量多打地过孔,间距最少1mm4.差分走线不满足间距规则5.网口两队差分需要控100欧姆,要添加class,进行等长,误差5mil6.电感所在层需要挖空处理7.注

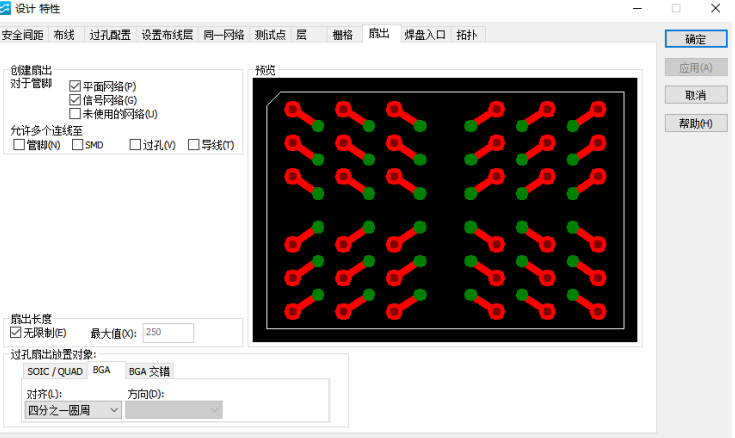

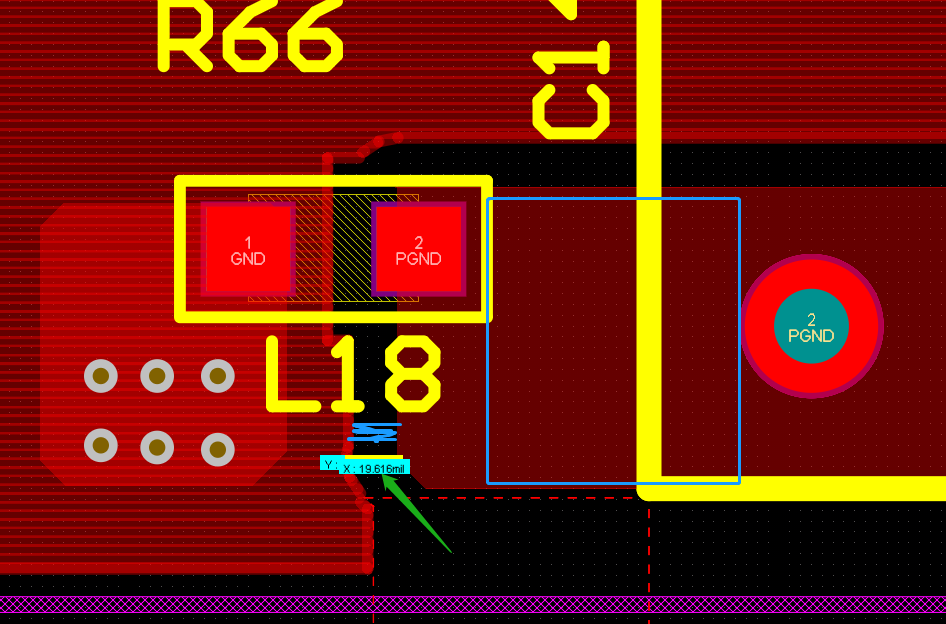

BGA扇出介绍

BGA扇出前须设置好规则,将BGA下方器件挪走,BGA下方所有层布线清除,若扇出时有DRC产生,会导致扇出失败。扇出前将格点设置为PIN间距的一半或者0,设置为PIN间距一半时须将精度设置好,否则会导到设置的格点4舍5入,设置失败。选择好合

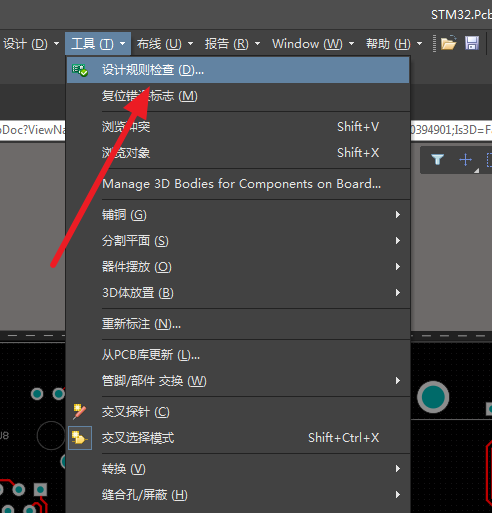

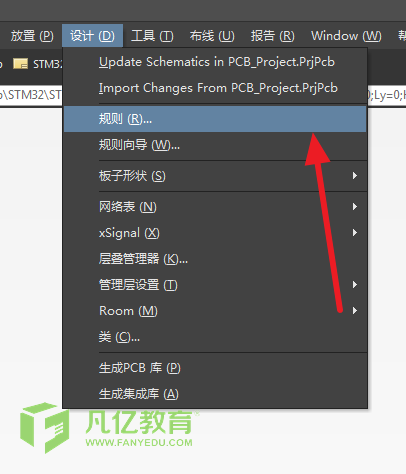

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

我们在进行PCB设计的时候,一定会碰到各种元素与各种元素之间的间距规则的设置。比如想要设置铜皮跟走线的间距,或者设置过孔跟丝印的间距。这些都涉及到我们最基本的PCB设计,所以足以看出这项技能在PCB设计中的重要性。

晶振注意包地:缝合孔不需要打太密集,间距150mil放置一个即可:过孔不要打在焊盘上,自己注意调整:多处存在这样的情况,自己更改。铺上铜皮就不用走线了:走线不能在器件内部:晶振是需要保持净空的,不能走线:以上评审报告来源于凡亿教育90天高速

差分需要按照阻抗线宽走2.跨接器件旁边要多打地过孔,间距建议2mm,有器件的地方可以不满足3.变压器需要所有层挖空处理4.网口除差分信号外,其他的都需要加粗到20mil,尽量单独打孔,器件靠近管脚摆放5.差分信号焊盘出线需要在优化一下6.晶

跨接器件旁边要多打地过孔,间距最少1.5mm,建议满足2mm,有器件的地方可以不满足2.网口差分需要进行对内等长,误差5mil3.模拟信号走线需要加粗,建议10-12mil4.反馈信号需要从电容后面取样,走10mil即可5.数据线之间等长需

扫码关注

扫码关注