- 全部

- 默认排序

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

关于信号完整性的绪论

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

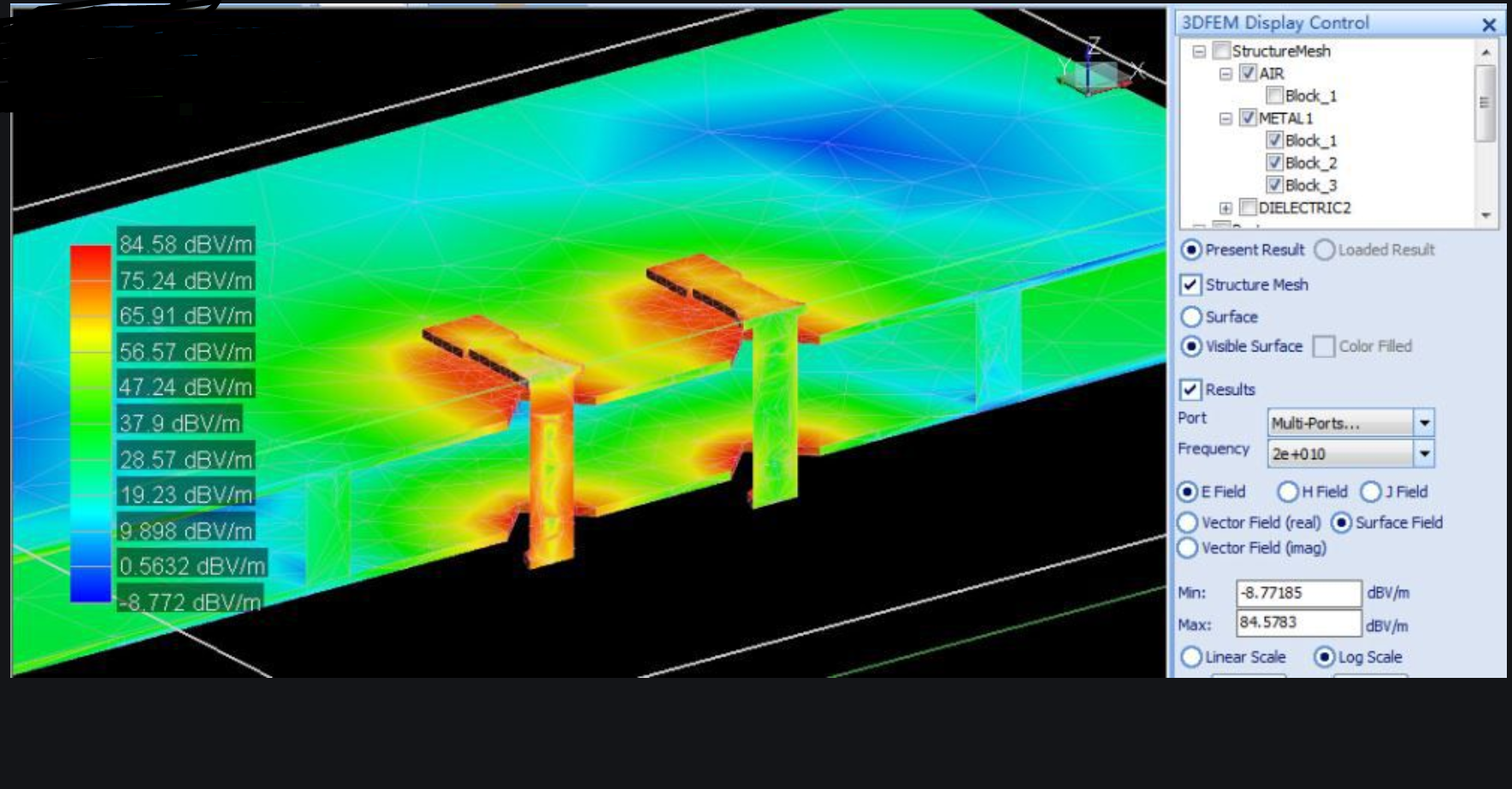

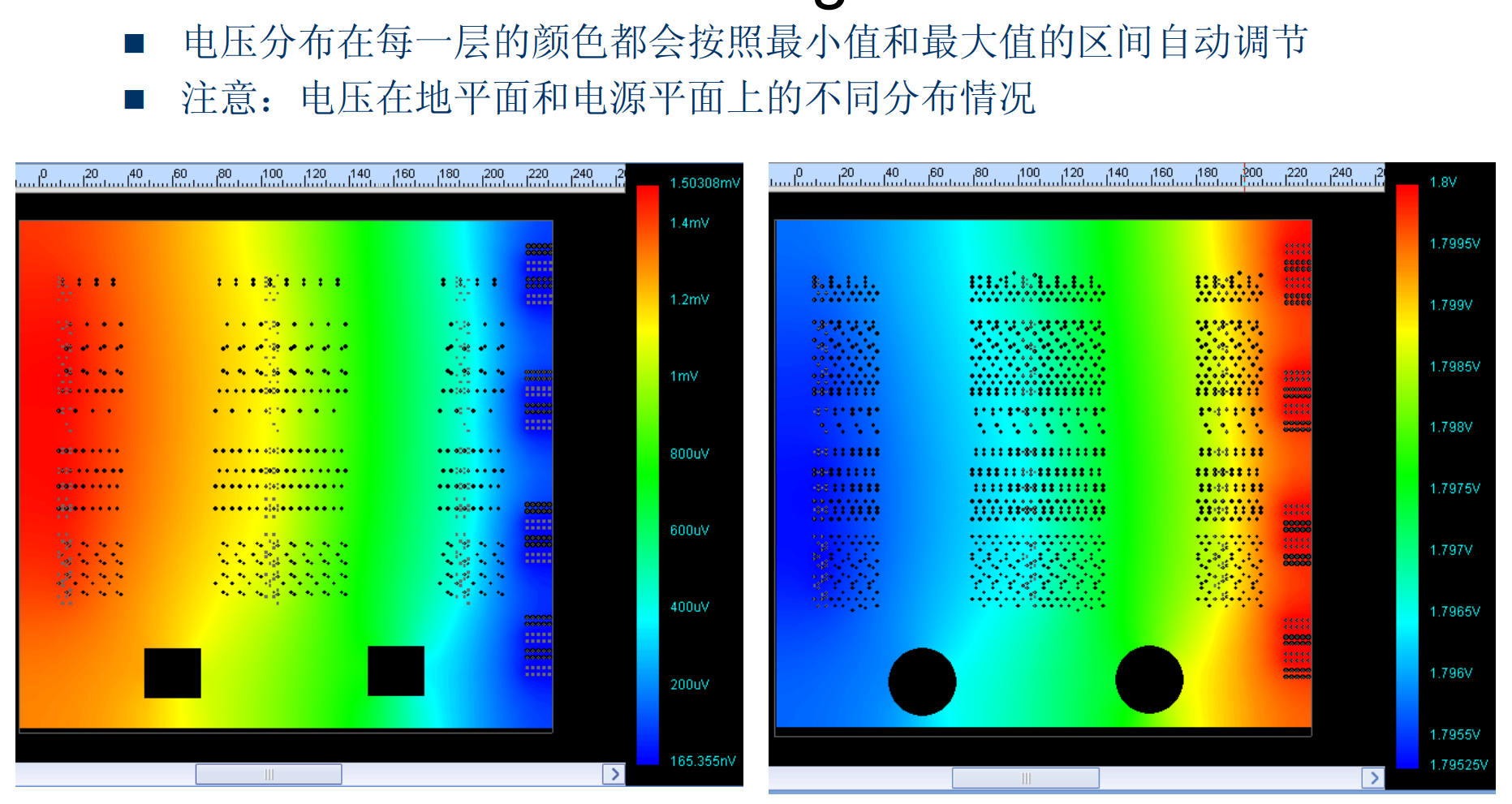

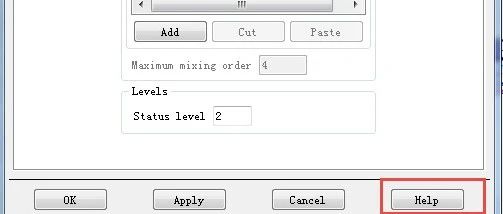

电压分布在每一层的颜色都会按照最小值和最大值的区间自动调节,注意:电压在地平面和电源平面上的不同分布情况 GND1 PO

复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence Sigrity高速信号仿真视频实战PCB仿真教程基础套餐 凡亿扫码添加助教小姐姐【备注:仿真基础】领取更多优惠复制这段话到TaoBao打开即可见↓4.0 hi:/信O3t7XoWNUQP信 Cadence

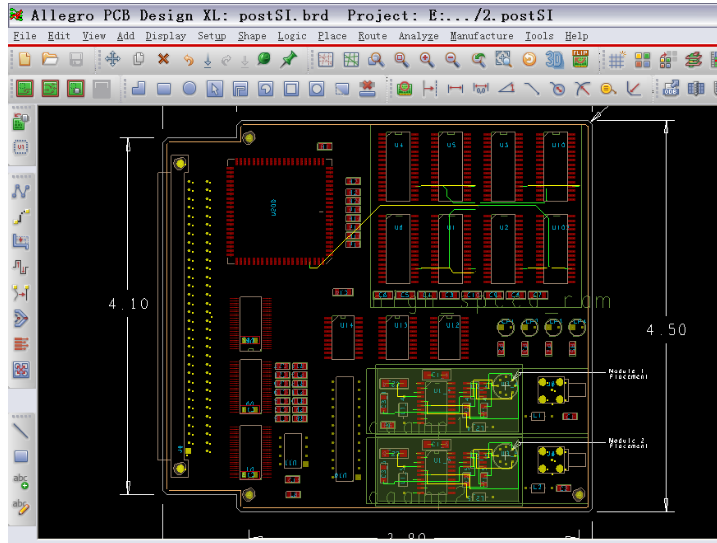

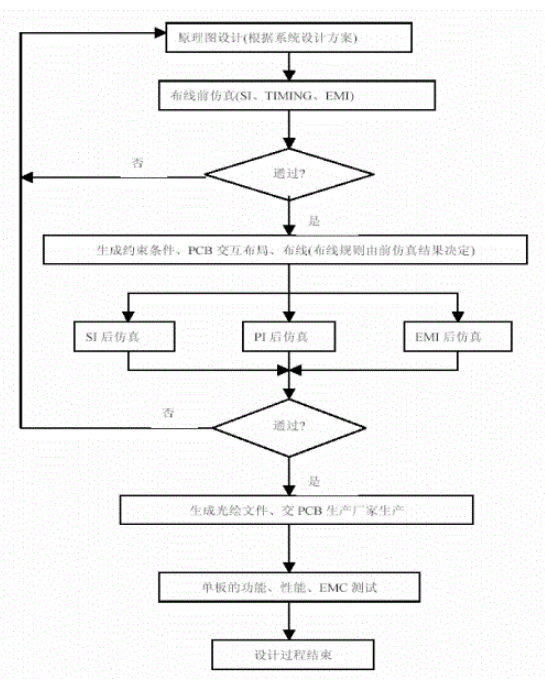

随着时代发展,电子设备的性能要求及数据处理量越来越严格,高速PCB设计已成为当下工程师的热门职业规划方向首选,那么若是要选择成为一名高速PCB设计工程师,自然也得了解高速PCB仿真设计的基本流程。如图所示:该图是PCB仿真设计的流程图。1、

在PCB设计中,仿真模拟是不可或缺的一环,工程师通过仿真模拟可预测电路的性能和行为,避免设计缺陷造成成本浪费,然而在市场上有很多不同功能及类型的仿真软件,如何挑选适合自己的仿真软件,已成为工程师需要思考的问题之一。首先,确定自己的需求和预算

说说仿真那些事

仿真,就是对实物进行建模,用模型来预测实际产品的性能。仿真的价值,在于可以缩短产品的研发周期,还有,可以弥补理论上的不足。 仿真想要预测的准,就要模型足够准确。这一大部分,是取决于仿真软件的准确度;另一小部分,则取决于仿真设置的正确性。 今天,就聊聊如何做好这一小部分。我ADS用的比较多,所以就以此

扫码关注

扫码关注