- 全部

- 默认排序

答:沿绝缘表面测得的两个导电零部件之间,在不同的使用情况下,由于导体周围的绝缘材料被电极化,导致绝缘材料呈现带电现象,此带电区的半径即为爬电间距。

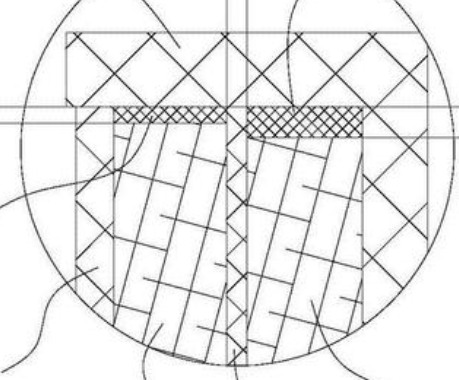

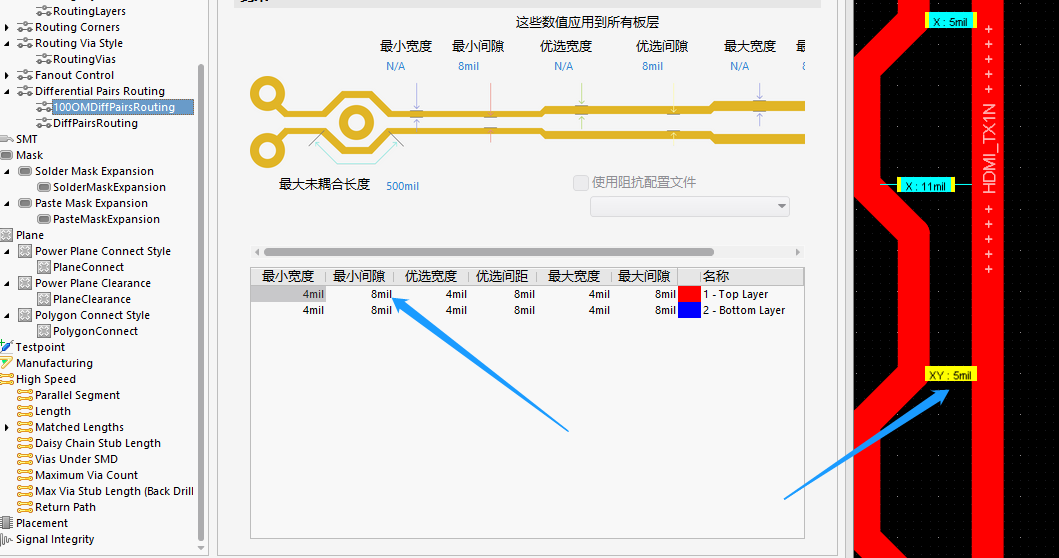

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

2、 广州PCB培训元器件封装 是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。 元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。因此在制作PCB板时必须同时知道元器件的名称和封装形式。 (1) 元器件封装分类

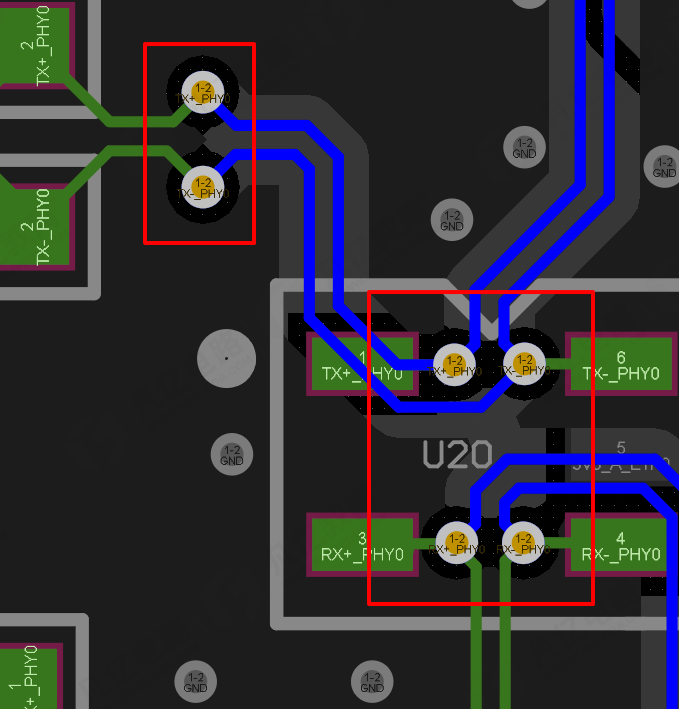

差分线对内等长凸起高度不能超过线距的两倍2.等长线之间尽量要满足3W规则,后期自己调整一下走线间距3.电源走线路径要尽量短,后期自己优化一下走线路径4.左右声道尽量单根包地5.差分走线要尽量耦合出线,后期自己调整一下地过孔6.注意天线部分挖

1.差分换层在旁边需要打回流地过孔2.差分对需要对内等长,差分出焊盘应尽快耦合3.信号线需要保持3w间距规则4.存在开路没有连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:ht

器件干涉2.地网络就近打孔,缩短回流路劲3.差分对内等长凸起高度不能超过线距的两倍4.差分走要耦合,且满足差分间距要求5.注意走线不要有直角,后期自己优化一下6.VREF的线宽最少要加粗到15mil以上7.差分对内等长误差5mil8.反馈线

差分走线不满足差分间距规则2.HDMI差分对内等长误差5mil3.确认一下此处是否满足载流,建议铺铜处理4.走线未连接到焊盘中心,存在开路5.差分出线要尽量耦合6.过孔尽量不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如

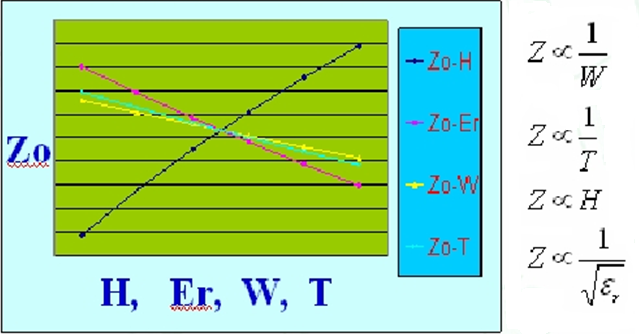

答:一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。

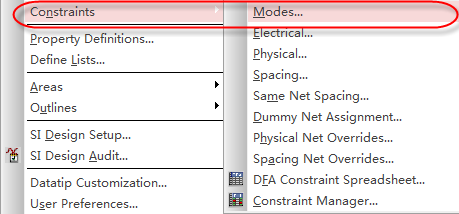

答:我们在PCB设计时,都会进行规则的设置,然后使用规则来约束设计,进行DRC的监测。我们这里讲解一下,soldemask也就是阻焊到其它元素的间距应该如何设置呢,具体操作的方法如下所示:

扫码关注

扫码关注