- 全部

- 默认排序

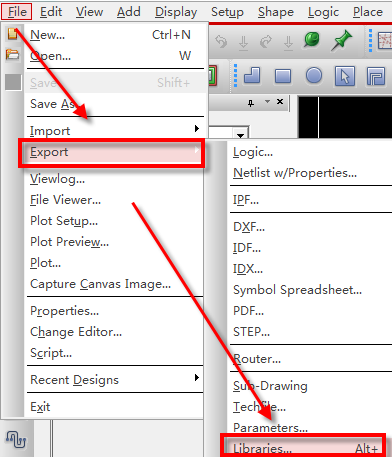

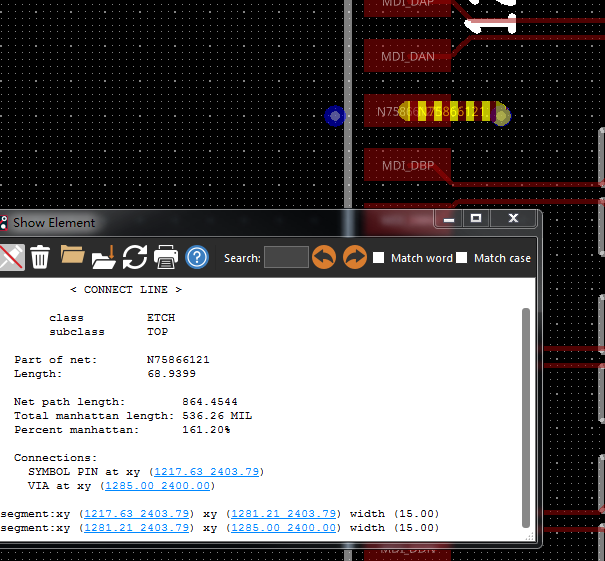

答:在导网表时,如果碰到有缺失Flash的报错,而正好缺失的Falsh在另一个项目中使用过,我们可以从另一个PCB中调用,具体的步骤如下:第一步,打开PCB,点击File-Export-Libraries…,在弹出的对话框中勾选Shape and flash symbols、No library dependencies选项,设置好导出的文件夹路径,点击Export导出,如图4-111所示;

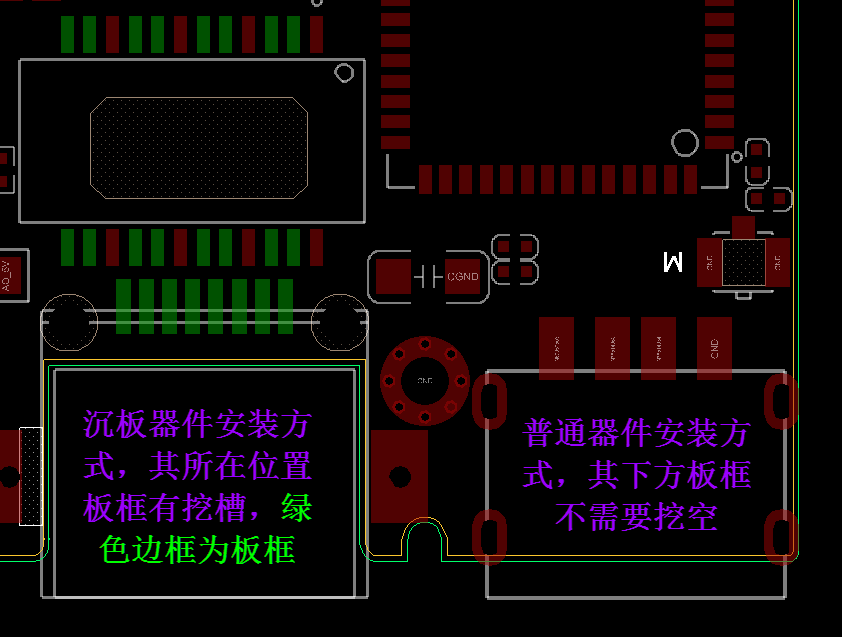

答:沉板器件即器件的管脚不是在其底部位置,是在它本体的中间位置,不像常规的器件一样,直接可以安装到PCB板子上,而是需要在PCB板子上进行挖槽处理,将其凸起的部分透过PCB板,让其管脚可以正常地贴装到PCB板子上,如图4-77所示: 图4-77 沉板器件处理示意图需要沉板处理的器件封装一般可按以下方法进行:Ø 开孔尺寸:器件四周开孔尺寸应保证比器件最大尺寸单边大0.2mm(8mil);保证能正常放进去。Ø 开孔尺寸标注:开孔标注通常标注在Board_Ge

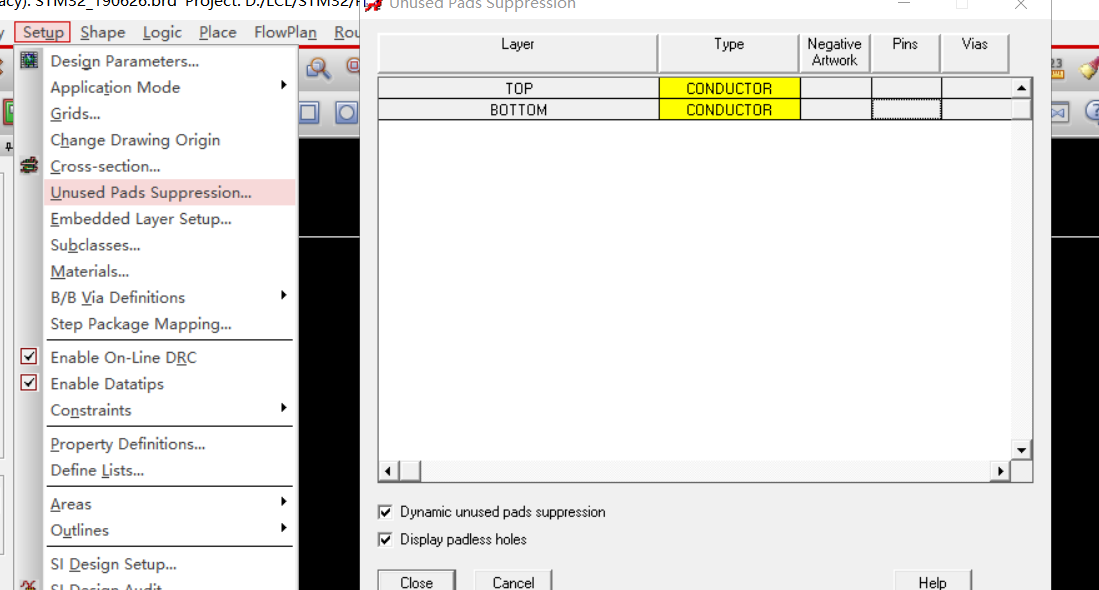

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,Allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

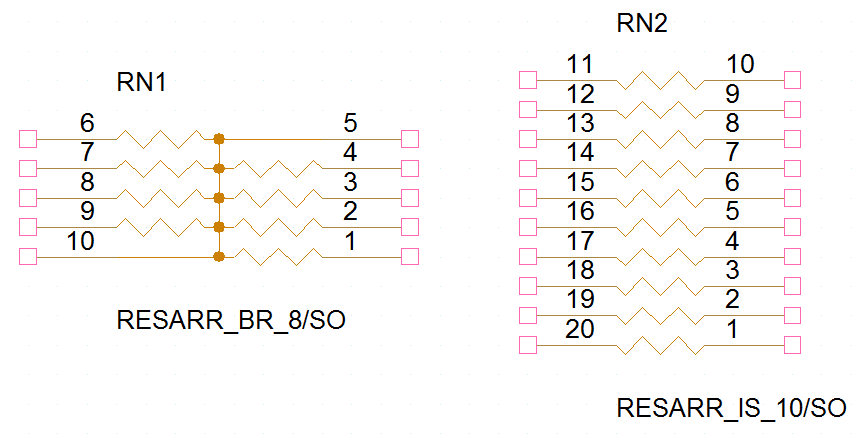

Allegro软件绘制PCB封装,比其它EDA软件相对于复杂一些,步骤更多一些,我们这里简单的列一下通过Allegro软件绘制的PCB封装的步骤。

Allegro经常导出STP文件后。用Catia无法打开是怎么回事?要不就是丢失部分铜皮。

修改封装的网络时,看不见十字大光标,看不见鼠标的移动使用16.6版本的Allegro,画封装时,界面的十字大光标就消失不见了,这个有补丁吗?

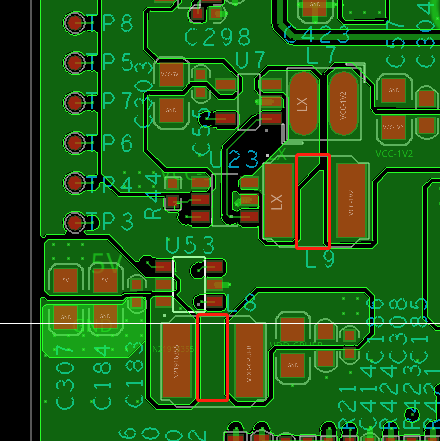

变压器除差分信号 其他信号20MIL:晶振注意做个包地:注意机壳地跟电路地在空间充足的情况下隔离2MM宽度:扇孔不整齐:差分以及RX TX等长没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

带你干所在层的内部需要挖空处理2.天线做隔层参考,需要挖空第二层3.差分对内等长处理不当,锯齿状凸起高度不能超过线距的两倍4.晶振需要走内差分,并包地,多打地过孔5.注意数据线等长需要满足3W规则6.地址线也需要满足3W规则7.网口差分需要

扫码关注

扫码关注