- 全部

- 默认排序

17.4制作pad命名时提示“Maximum padstack name is 15 characters”,最大padstack名称为15个字符,可以忽略吗?

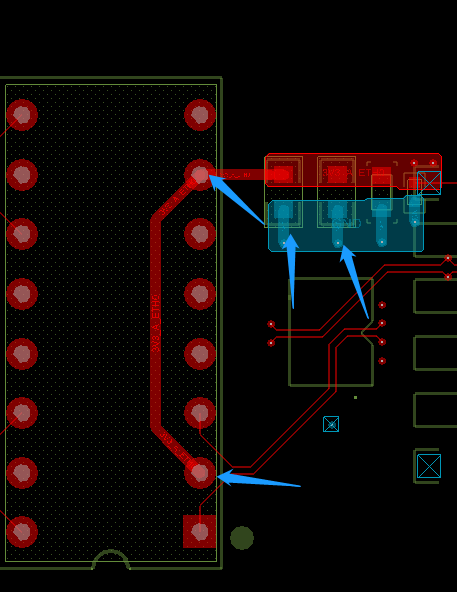

电容尽量靠近管脚放置,一个管脚一个2.百兆网口差分需要进行对内等长,误差5mil,差分尽量少换层打孔3.RX和TX需要添加等长组进行等长,误差100mil4.电容靠近管脚放置5.确认一下此处是否满足载流,注意电源要满足载流6.器件摆放尽量中

Allegro作为一款功能强大的电子自动化设计(EDA)工具,广泛应用在电子设计领域,然而,由于其复杂的功能和操作,工程师在使用Allegro软件可能会遇见各种各样的问题,其中之一是如何进行3D模型设计?本文将针对这各问题进行回答,希望对小

网口差分走线要尽量耦合2.其他信号需要加粗到20mil3.变压器靠近网口放置,并且变压器所有层挖空4.器件摆放尽量对齐处理5.HDMI需要进行等长,对内误差5mil,对间10mil6.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产

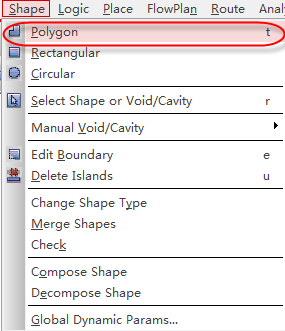

答:我们在PCB设计中经常听到需要漏铜处理,或者是这里我要铺白油,这在PCB板上非常好理解,生产出来黄色的就是铜,白色一块的就是白油。我们这里讲解一下,在Allegro软件中如何处理,具体操作如下所示:

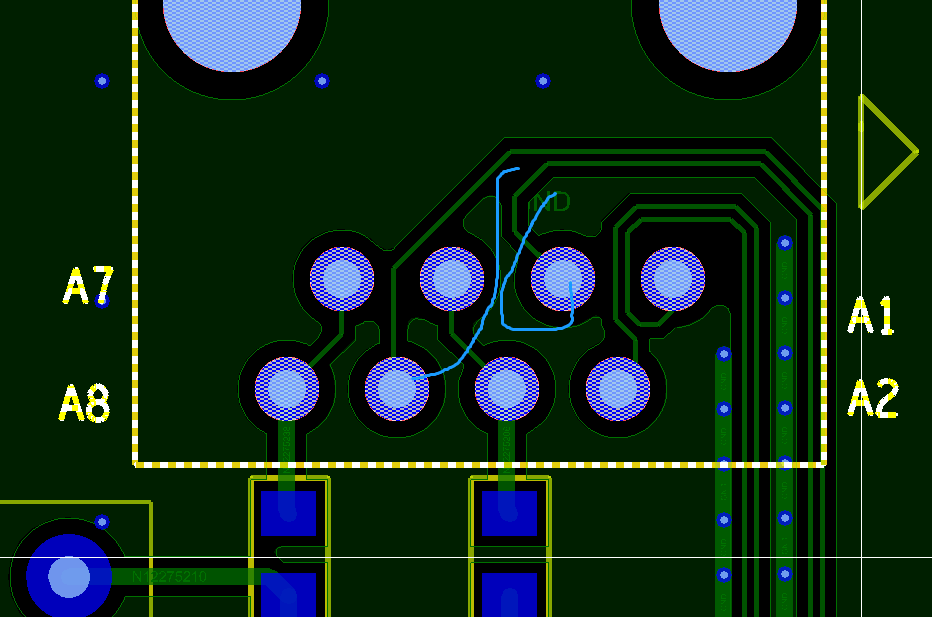

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

扫码关注

扫码关注