- 全部

- 默认排序

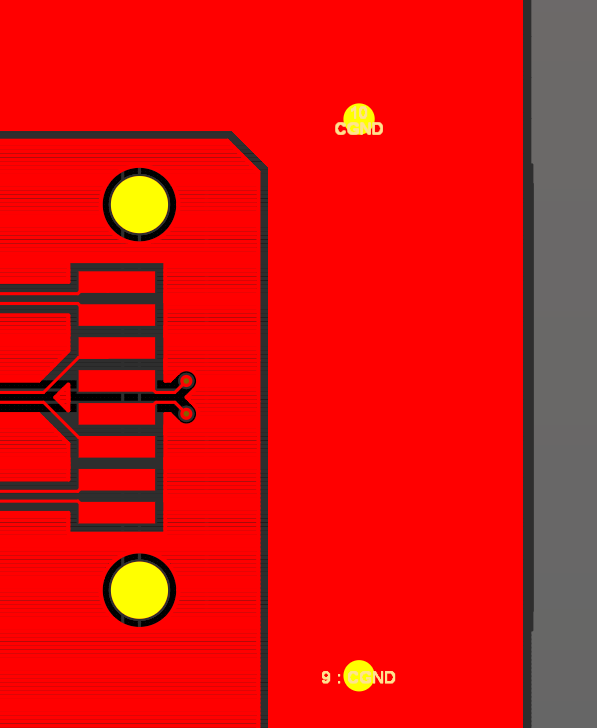

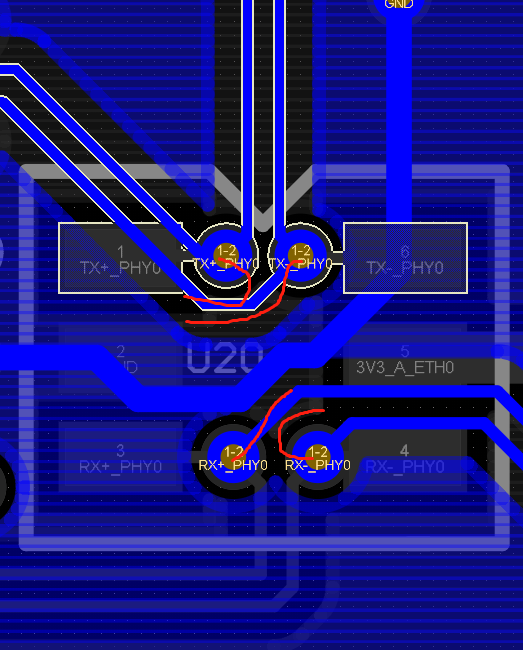

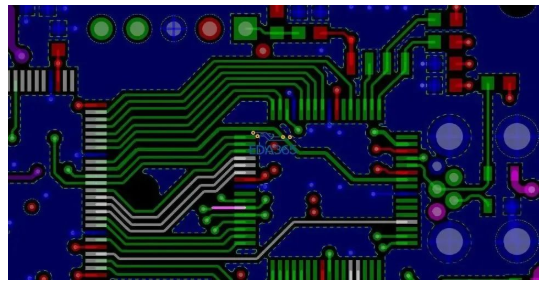

机壳地跟电路地之间需要满足2MM间距:跨接器件两边可以都打点地过孔:板上这种孤铜需要割除,其他地方一致情况的自己去修改:变压器上除了差分信号,其他的信号加粗20MI走线:注意差分走线是连接到焊盘中心的:注意差分走线连接焊盘还可以优化:差分走

差分走线要注意耦合出线2.时钟信号包地需要再地线上打上地过孔3.差分走线不满足间距规则4.网口差分需要进行对内等长,误差5mil5.小块孤铜后期可以挖掉以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

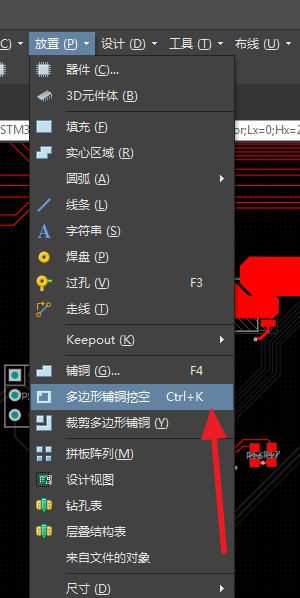

有时候在进行PCB设计的时候,特别是在进行敷铜之后,还需要我们去删除一些孤铜,尖刺的铜皮。那么就要进行我们的CUTOUT功能了。其功能就是禁止铜敷进有防止过CUTOUT的区域,这个只是针对于敷铜有效,它不能作为一个独立的铜存在,所以我们放置完CUTOUT之后是不用进行删除的。

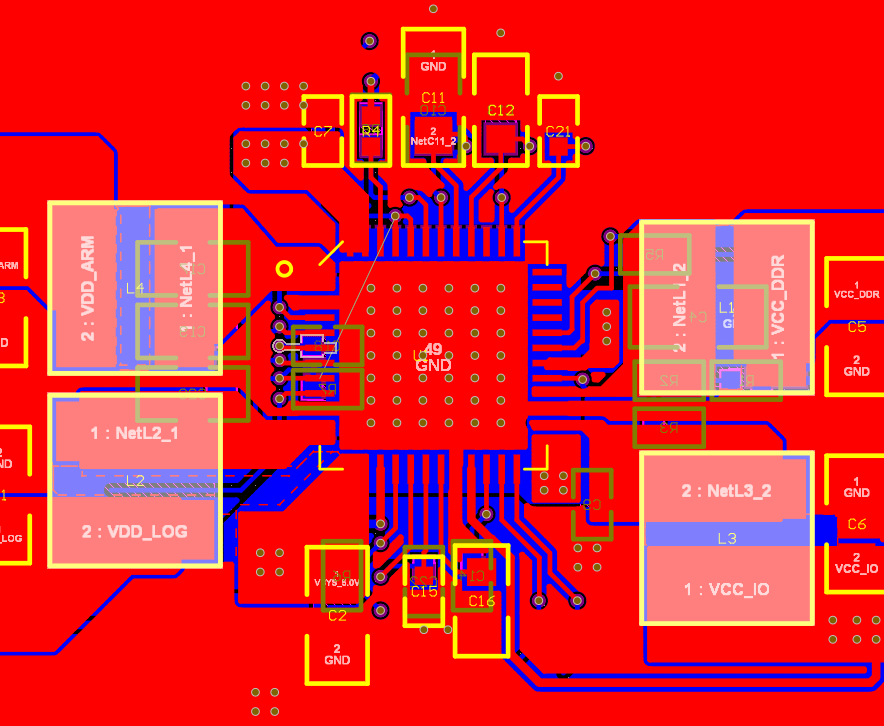

电感底部不能放置器件以及走线,重新布局下,可以将电容塞到芯片底部:这种孤铜都去除下:走线注意规范不要出现锐角以及直角:DCDC输出主干道的铜皮尽量加宽一点:放置完铜皮挖空之后需要重新灌铜才能自动避让挖空区域:反馈信号走线又是直角:铺铜也注意

有时候在进行PCB设计的时候,特别是在进行敷铜之后,还需要我们去删除一些孤铜,尖刺的铜皮。那么就要进行我们的CUTOUT功能了。其功能就是禁止铜敷进有防止过CUTOUT的区域,这个只是针对于敷铜有效,它不能作为一个独立的铜存在,所以我们放置完CUTOUT之后是不用进行删除的。

你知道PCB设计是不是该去除孤铜?PCB设计的技巧需要注意很多问题,各个器件的兼容问题,以及成品问题等等都是需要考虑的重要因素。我们今天的主题是PCB设计的时候是不是该去除孤铜的问题?有人说应该除去,原因大概是:会造成EMI问题。增强搞干扰

扫码关注

扫码关注