- 全部

- 默认排序

在我们进行PCB设计的时候,阻焊规则的设置就是设置焊盘到绿油的距离。因为我们在电路板制作的时候,阻焊层要预留一部分的距离和空间出来给焊盘,以致于绿油不至于覆盖到焊盘上去,造成锡膏无法上锡到焊盘。那么这个距离的延伸量就是放置绿油和焊盘相重叠。所以阻焊规则的重要性也是无需质疑的了。

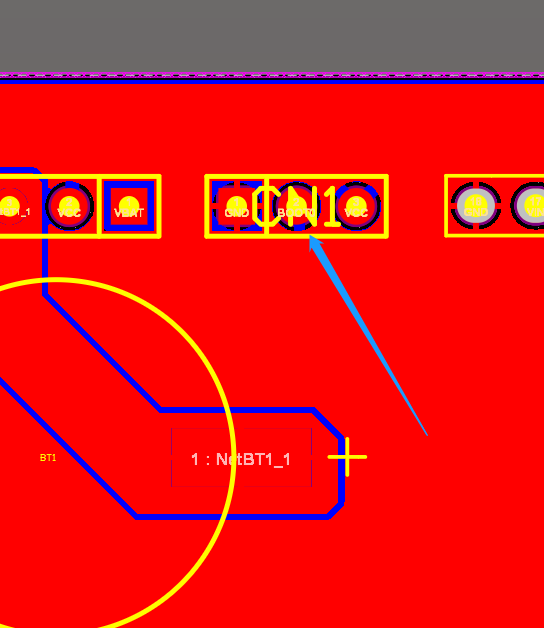

我们有时在进行PCB设计的时候,肯定会选择直接拖动 一个元器件或者一个模块去进行自己想要的布局。那么,就会遇到我们在拖动的时候,这个元器件或者这个模块是高亮,但是其它元器件与区域全部都是完全黑暗的,我们根本都看不清楚,此刻拖动的元器件或者模块被放置在哪里了,是不是重叠了其它的元器件放置。所以,遇到这个问题,我们应该如何解决呢?

Cadence 17.4 画好 Symbol 后,Pin Name 总是挤在一起(已经调整N遍,更新库文件了)这个有解吗

还存在网络并未连接完全,自己后期铺地铜进行连接:注意调整下器件位号丝印,不要覆盖在焊盘上或者是重叠,直接就近放在器件旁边整齐排列即可:过孔散热焊盘上的开窗即可,其他的盖油处理:铺铜注意不要有这种尖角:电感内部注意挖空处理:自己看下过孔都没网

器件位号丝印后期设计完成需要调整,不要重叠:注意板上过孔是否盖油,不要开窗:注意看下工程里面原理图是空的:铺铜注意按照左边钝角绘制,不要直角:可以优化。类似的情况自己优化下。注意晶振底部不要走线:建议是PCB板框放在机械层:器件位号都放到器

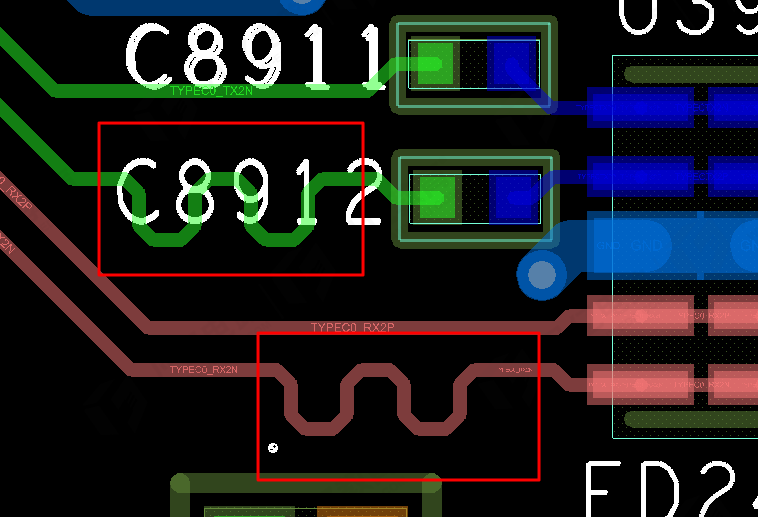

1.差分对内等长不规范2.差分走线不规范,出焊盘后应该尽量耦合,后面两个电容可以布局到背面。3.这里是兼容设计,上下两个电阻应该叠放到中间器件焊盘上,以保证差分和电阻的连接不受影响。4.差分走线不耦合,没有按照差分布线间距走线5.过孔重叠以

扫码关注

扫码关注