- 全部

- 默认排序

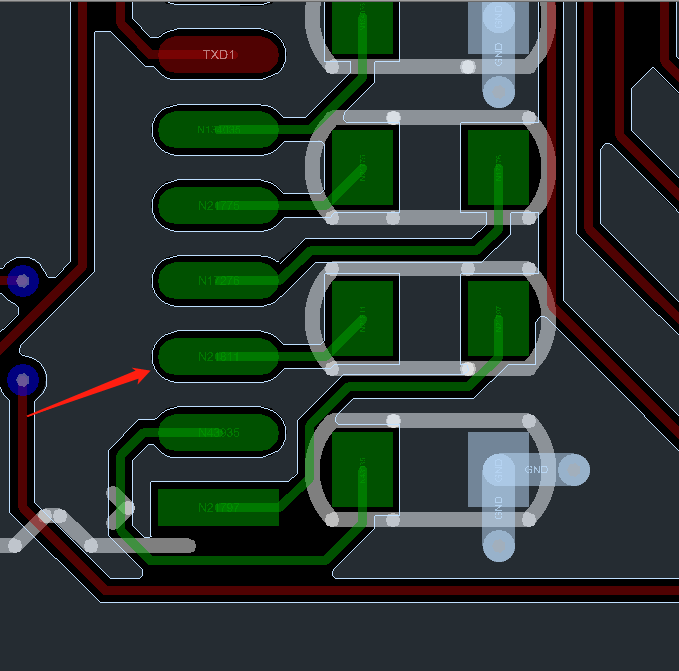

注意单点接地,此处不用打孔,只需要在芯片中心打孔进行回流即可2.电感所在层的内部需要挖空处理3.器件摆放注意对齐4.走线可以离测试点远点,后期自己调整一下走线路径5.反馈线走10mil即可6.注意电源输入需要打孔在底层进行连接输出打孔打在滤

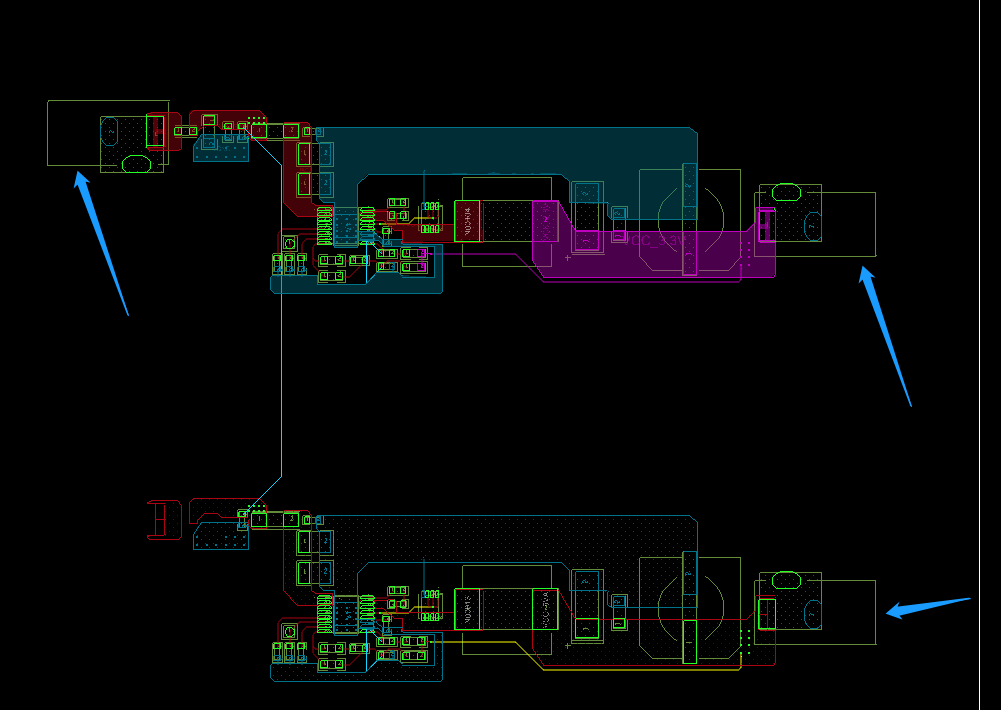

RS232的升压电容走线需要加粗2.电源输出打孔要打在滤波电容后面3.SD需要创建等长组进行等长,误差范围300mil4.以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

座子需要靠近板框放置2.滤波电容放置要保持先大后小原则3.反馈线需要走一根10mil的线4.打孔要打在滤波电容的前面5.电源主干道需要再底层铺铜进行连接,不要有开路6.走线尽量不要有锐角7.电感下面尽量不要走线,反馈尽量远离电感,电感所在层

USB的差分信号需要进行对内等长,等长误差为5mil2.晶振走线需要走类差分处理3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.电源输出部

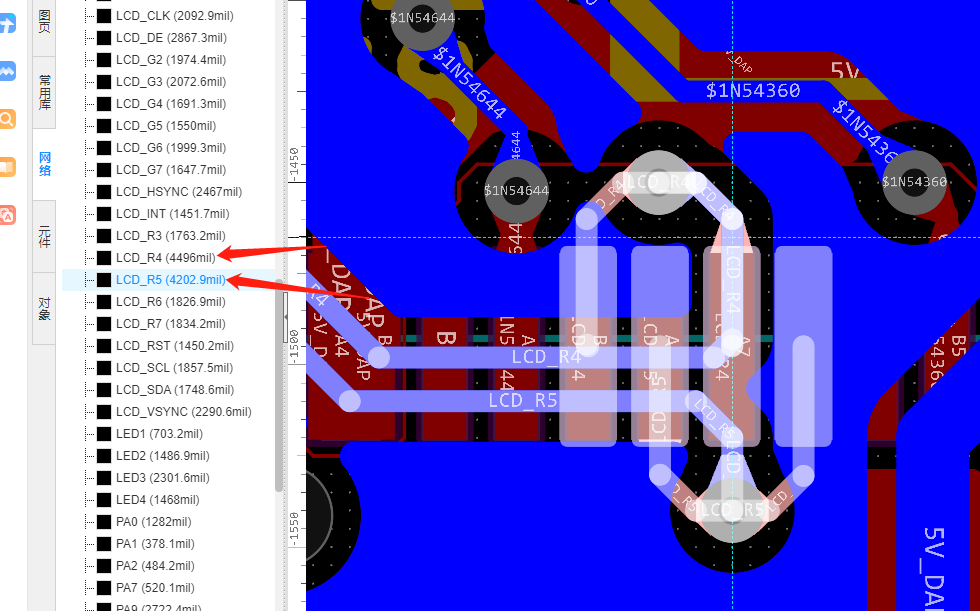

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

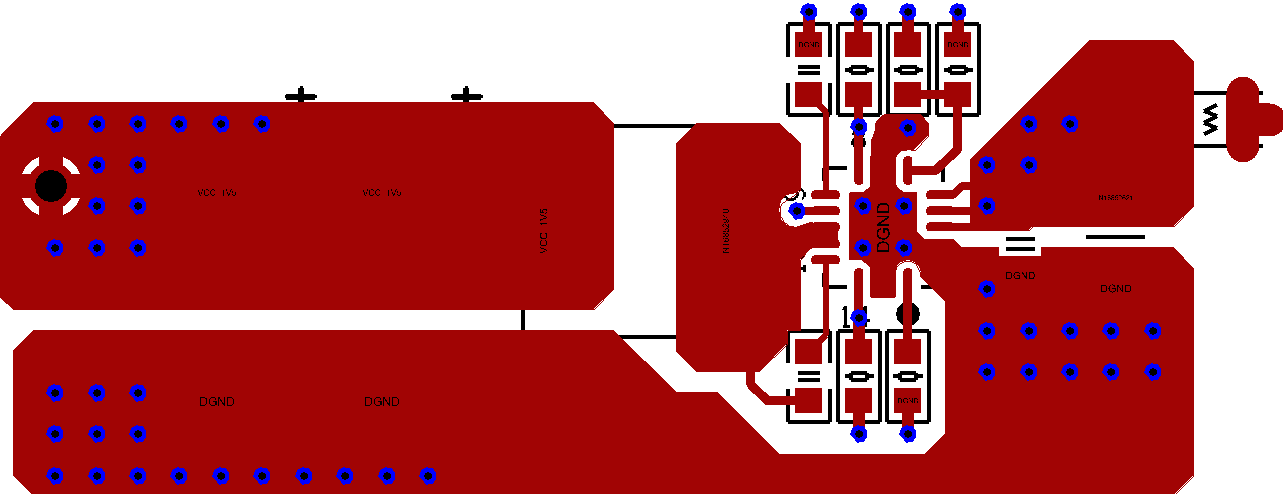

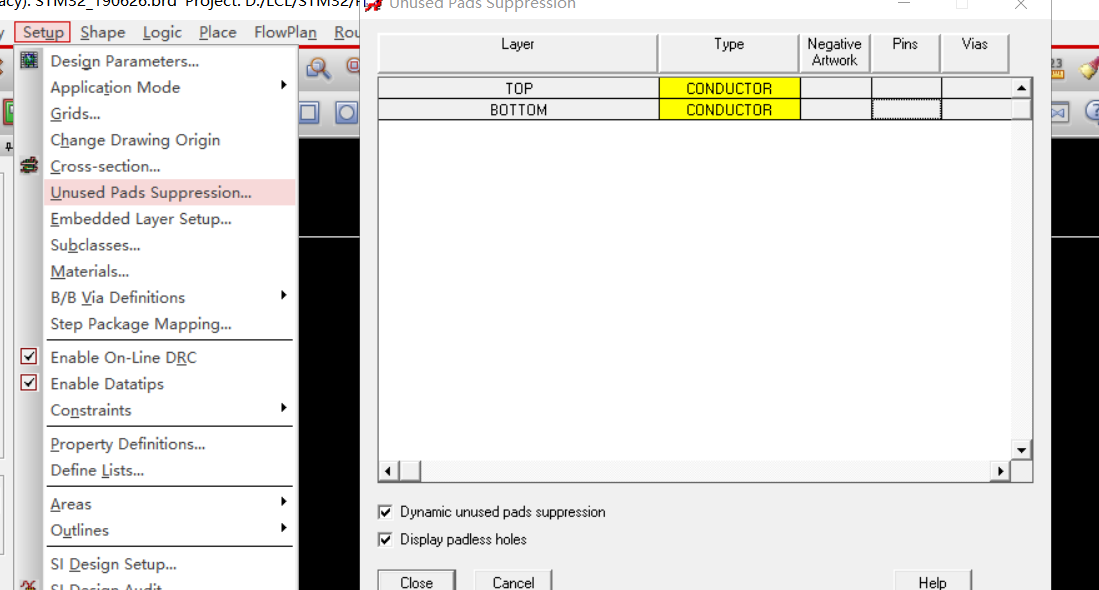

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

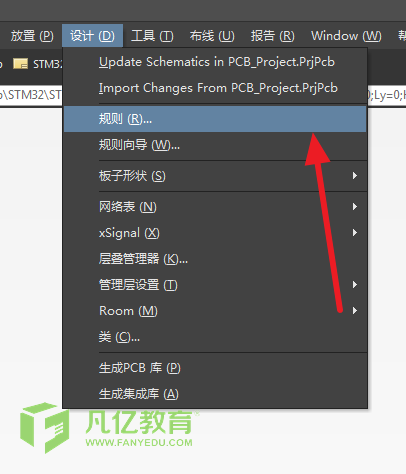

我们在进行PCB设计的时候,一定会碰到各种元素与各种元素之间的间距规则的设置。比如想要设置铜皮跟走线的间距,或者设置过孔跟丝印的间距。这些都涉及到我们最基本的PCB设计,所以足以看出这项技能在PCB设计中的重要性。

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

扫码关注

扫码关注