- 全部

- 默认排序

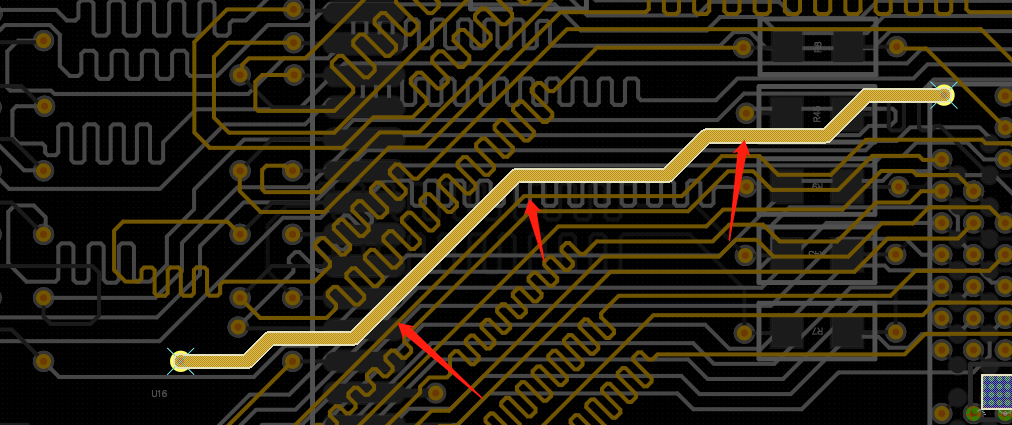

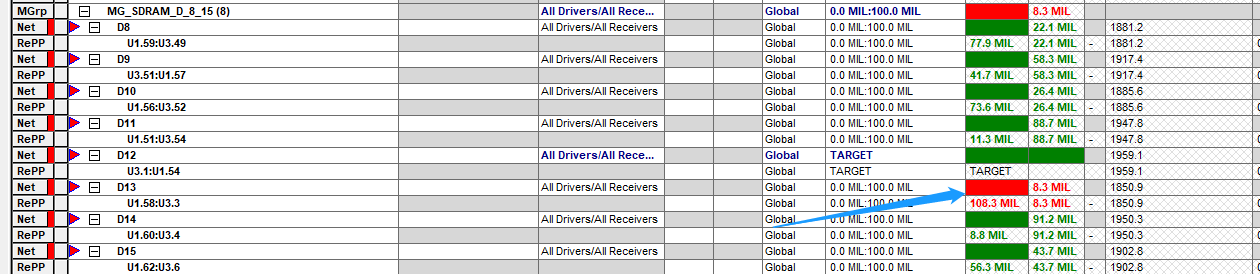

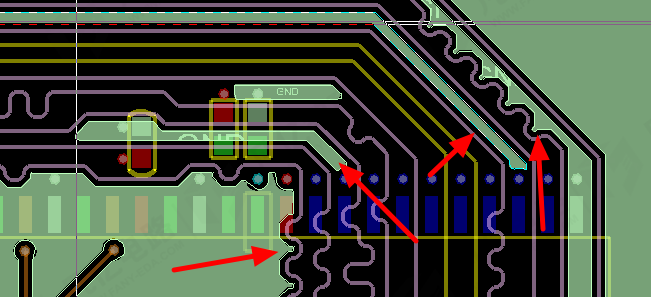

数据线与地址线之间的分割线上需要打地过孔,建议150mil一个第4层数据线和地址线之间也需要添加一根地线分开2.等长存在误差报错3.有器件连接的网络要创建Xsignals进行等长4.注意电源需要再电源层处理一下,铺铜进行连接5.注意器件不要

1SDRAM注意数据线等长存在报错2DDR注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

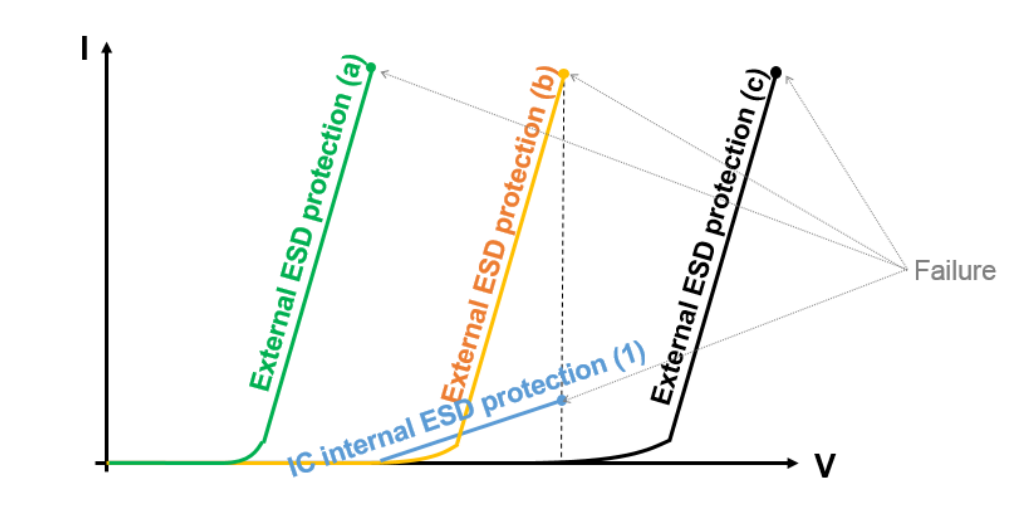

电路设计防静电原理解析

一、静电放电波形和能量频谱 静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前辈电路设计了很多静电放电模型。 常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规

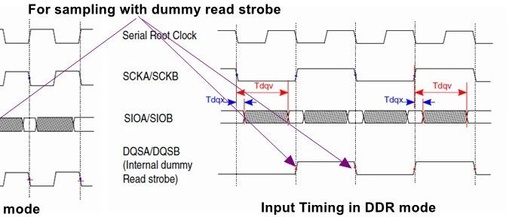

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是在FDCB里使能串行NOR Flash的DTR模式。前两篇文章 《IS25WP系列Dummy Cycle设置》 与 《IS25LP系列Dummy Cycle设置》, 痞子衡均是设置Flash的Fast Read Quad I/O SDR

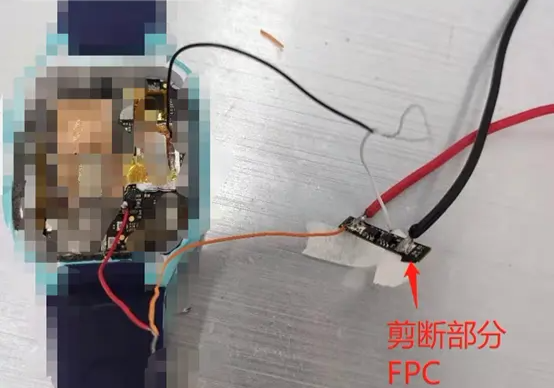

某智能手表在侧键附近打ESD后出现反复开关机现象根据反复重启的时间判断,类似于长按Power键。检查Power_On信号,发现已经被持续拉低,Power_On信号的原理图如下:为了降成本,位置1并没有贴TVS管,而是用一个电容代替,电容的耐

Micro SD卡是一种极细小的快闪存储器卡,其格式源自SanDisk创造,原本这种记忆卡称为T-Flash,及后改称为Trans Flash;而重新命名为Micro SD的原因是因为被SD协会 (SDA) 采立。另一些被SDA采立的记忆卡包括Mini SD和SD卡。其主要应用于移动电话,但因它的体积微小和储存容量的不断提高,已经使用于GPS设备、便携式音乐播放器和一些快闪存储器盘中。

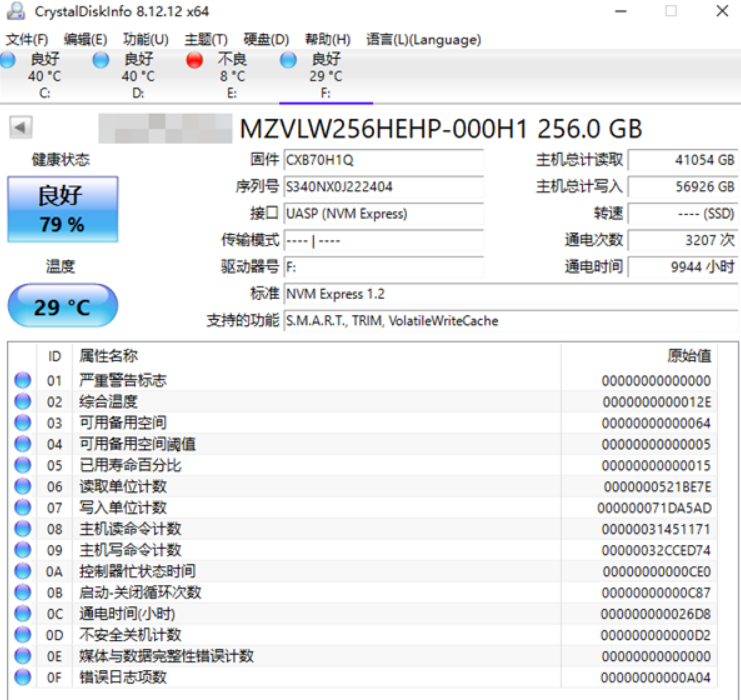

最近在贴吧和一些相关论坛中,有关固态硬盘“0E”的讨论成为热门话题,讨论指向某些型号的NVMe固态硬盘正频繁出现S.M.A.R.T.信息中“0E”与“03”两项的异常值,而这两个现象意味着这类NVM存储介质正在出现非正常寿命损耗范畴内的“坏

直播介绍:DDR SDRAM高速存储器是在高速PCB设计当中常见的模块,很多工程师对于如何处理单片、两片以及多片的布局、布线设计有很大的困惑,是一个设计难点。开设本次直播旨在全方位、多层次的去介绍DDR SDRAM高速存储器以及设计思路。直

扫码关注

扫码关注