- 全部

- 默认排序

随着半导体技术高速发展,越来越多电子产品迭代更新速度加快,高速度的数据传输及内存支持,这些都离不开DDR产品的支持,DDR产品已成为了大部分电子工程师的日常设计产品之一。然而DDR产品的设计是具有挑战性的,因为它涉及到高速数字电路和复杂的时

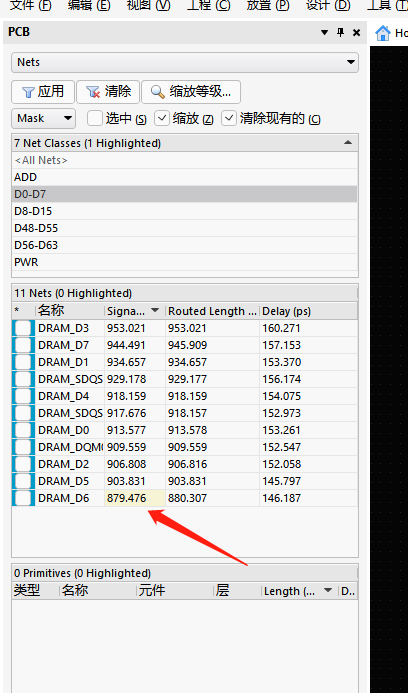

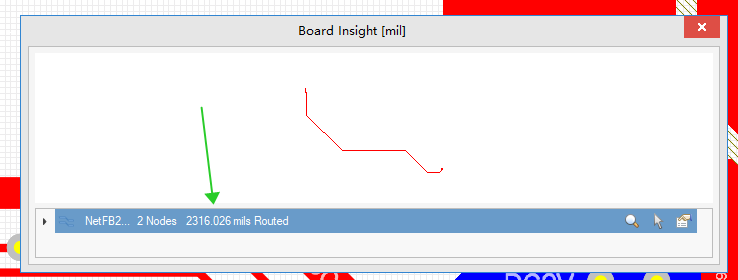

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

一个layout工程师学习信号完整性之路刚开始听说和接触眼图时,是从DDR的仿真眼图开始的,看到别人的仿真结果,很是羡慕。然后自己开始仿真研究,设计PCB单板,提取S参数,使用ADS、SPEED2000、Ansys搭建电路,设置参数,调试仿

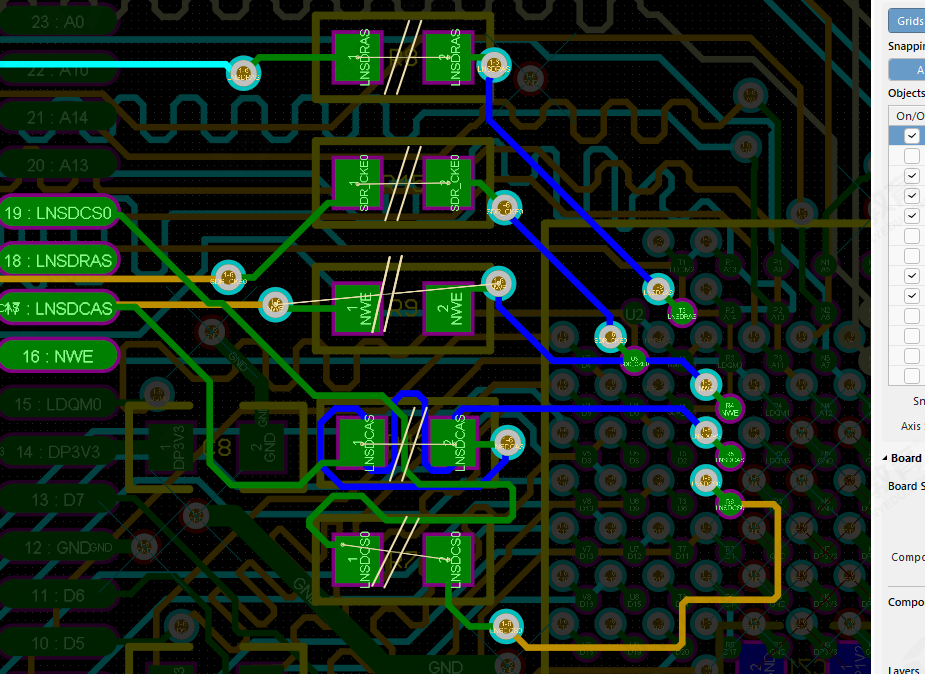

数据线等长存在报错2.走线尽量不要走直角,建议钝角3.此处走线需要优化一下4.走线未连接到过孔中心,存在开路5.此处出线载流瓶颈,自己加宽铜皮6.注意过孔不要上焊盘7.地和电源都需要加粗8.地就近打孔,缩短回流路劲9.差分出线要尽量耦合10

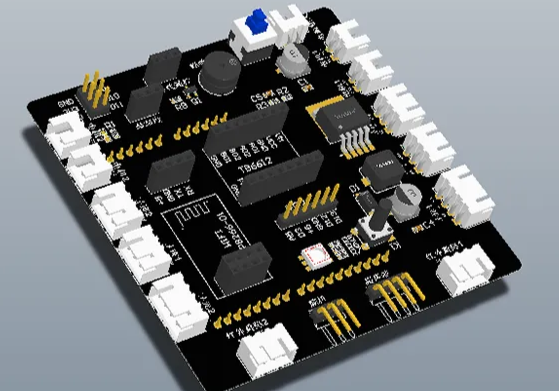

多处存在开路报错焊盘应从短边出线,避免从长边和四角出线DDR和芯片放置太近,导致没有足够空间绕线,绕线很乱走线不能从同层器件中间穿过时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

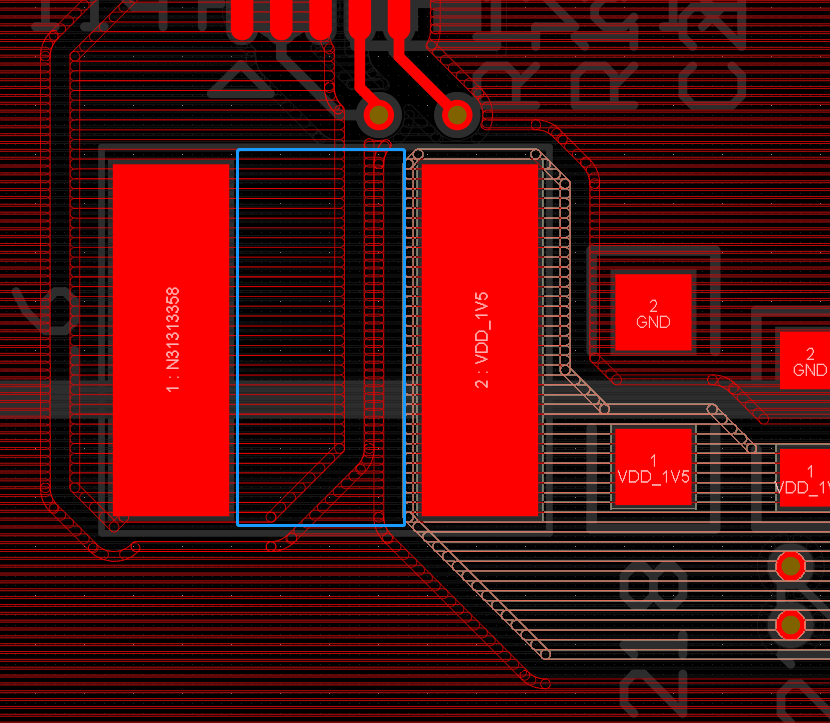

电感所在层的内部需要挖空处理2.反馈线走一根10mil的线即可,不用进行铺铜3.存在开路4.地址线等长存在报错5.注意电源线宽尽量保持一下,满足载流,走线最少需要加粗到15mil以上6.地网络需要就近打孔以上评审报告来源于凡亿教育90天高速

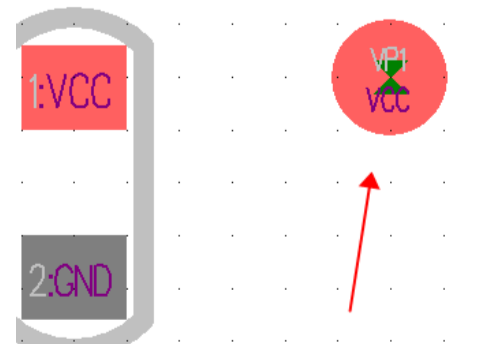

虚拟过孔也被称为T点或者是分支点,可以定义一个点,通常是从驱动器到这个点“分支”出去到多个接受器,进一步增强了PADS中多片DDR走线方面的功能。我们可以定义特殊的间距和高速设计规则到这个新的拓扑结构。在PCB的空白处,点击鼠标右键,在弹出

扫码关注

扫码关注

![[答疑]DDR设计需要背钻吗](https://api.fanyedu.com/library/images/202308//8855dc55f219930efe666de94c8c4fda.png)