- 全部

- 默认排序

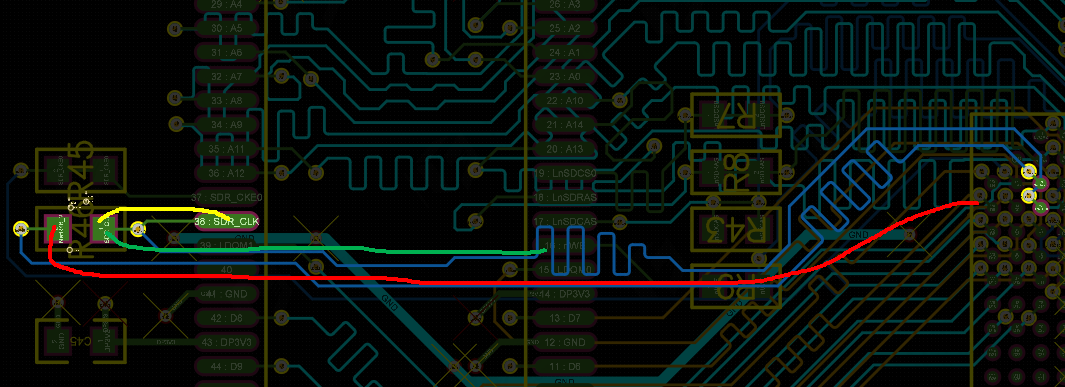

时钟线等长错误等长组分类缺少网络等长绕线太乱,太不均匀,锯齿状绕线应尽量上下咬合电源管脚配置电容应靠近引脚放置,均匀分布在焊盘旁边就近连接焊盘等长绕线角度太小,实际生产会是直角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

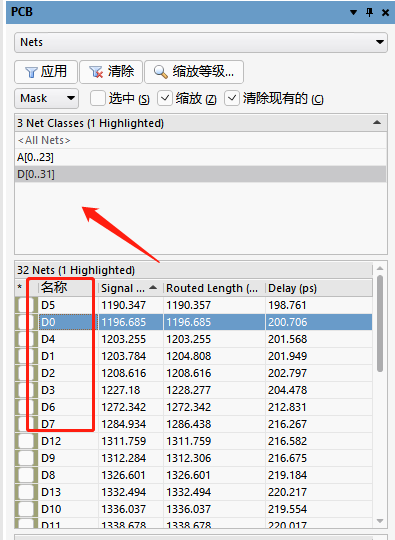

器件尽量整体中心对齐:等长线的gap大于等于3W:地址数据等长误差没什么问题 ,都在误差范围内:其他的基本没什么问题,完成得还可以。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

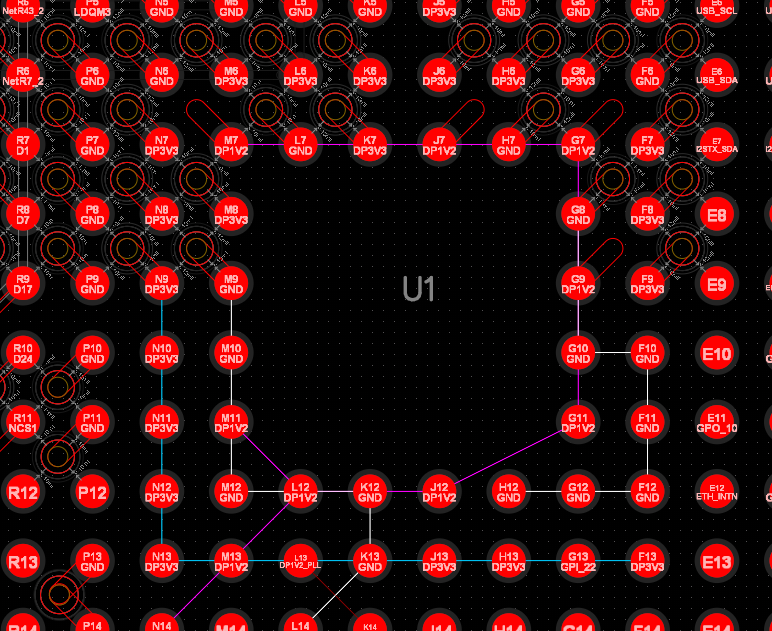

数据线高八位和低八位要分别进行分组等长,一组9根2.地址线等长不符合原理图要求3.等长注意一下不要有直角4.地址线分组需要把时钟信号,读写,控制都添加进来以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

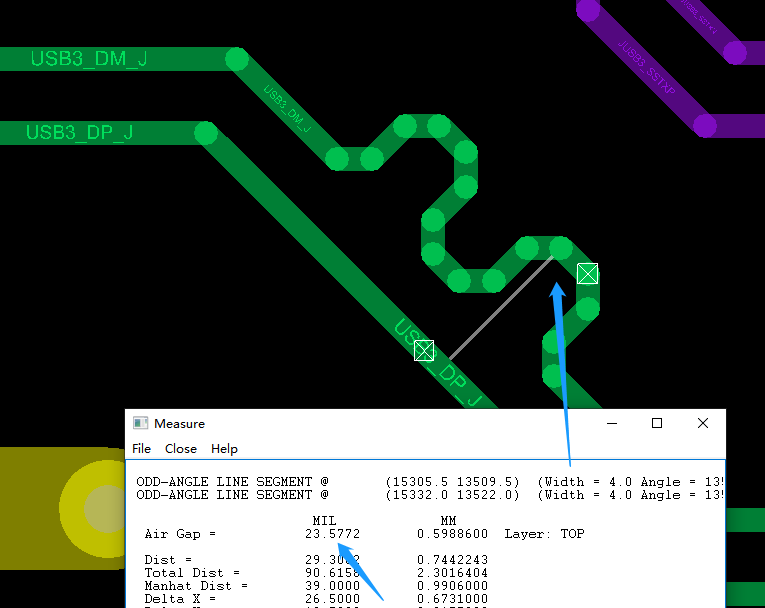

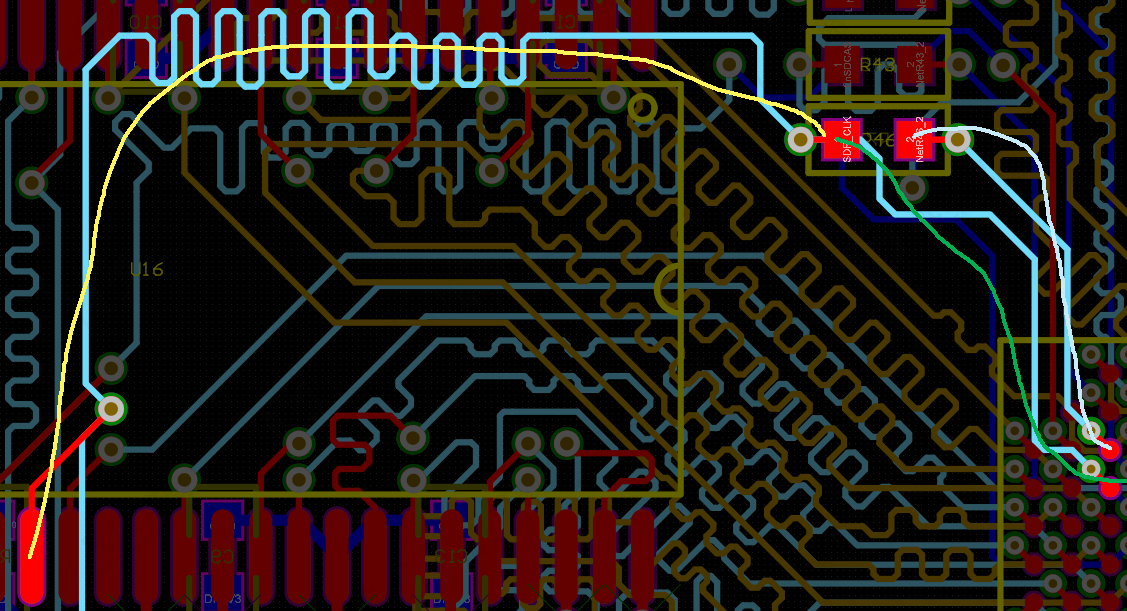

锯齿状等长不能超过线距的两倍很多差分都存在相同的问题,后期自己修改一下2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.CC1属于重要信号,需要加粗处理4.ESD器件尽量靠近座子管脚放置5.差分出线要尽量耦合6.器件摆

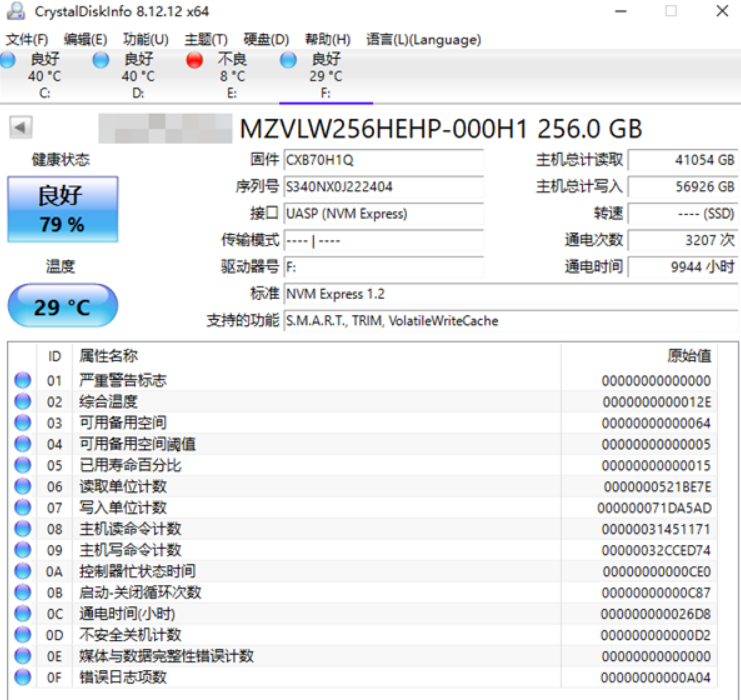

最近在贴吧和一些相关论坛中,有关固态硬盘“0E”的讨论成为热门话题,讨论指向某些型号的NVMe固态硬盘正频繁出现S.M.A.R.T.信息中“0E”与“03”两项的异常值,而这两个现象意味着这类NVM存储介质正在出现非正常寿命损耗范畴内的“坏

时钟信号等长错误数据线分组却少网络等长绕线太丑,信号流向尽量顺畅以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

差分对内等长误差器件顺序不对应该先经过eSD在经过电阻USB3.0:差分包地每组都要包地的地线上要打回流地过孔差分对内没有做等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:ht

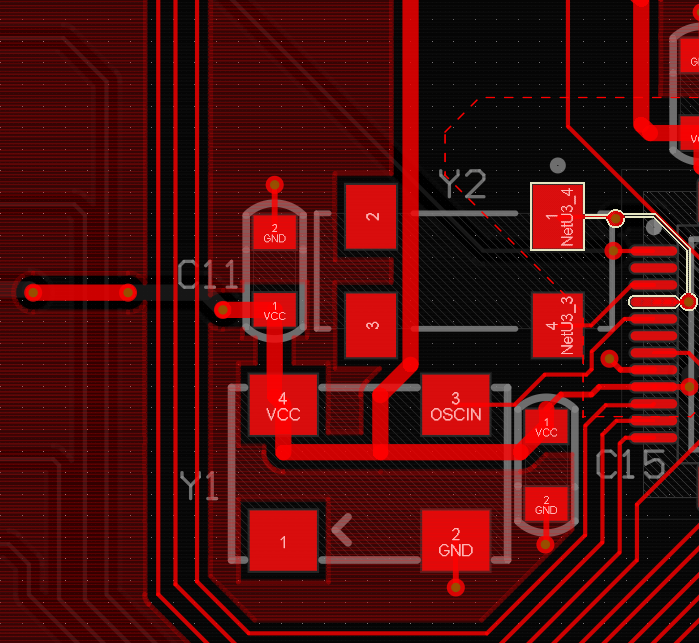

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

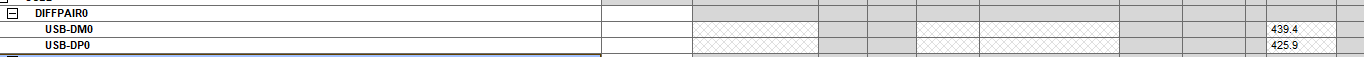

晶振需要包地处理2.此处一层连通无需打孔3.差分换层尽量在旁边打上一对地过孔,空间足够尽量包地处理4.差分出线尽量耦合5.长焊盘出线不规范,尽量从中间拉出来在耦合6.注意过孔不要上焊盘7.SD卡未添加class进行等长,误差300mil8.

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注