- 全部

- 默认排序

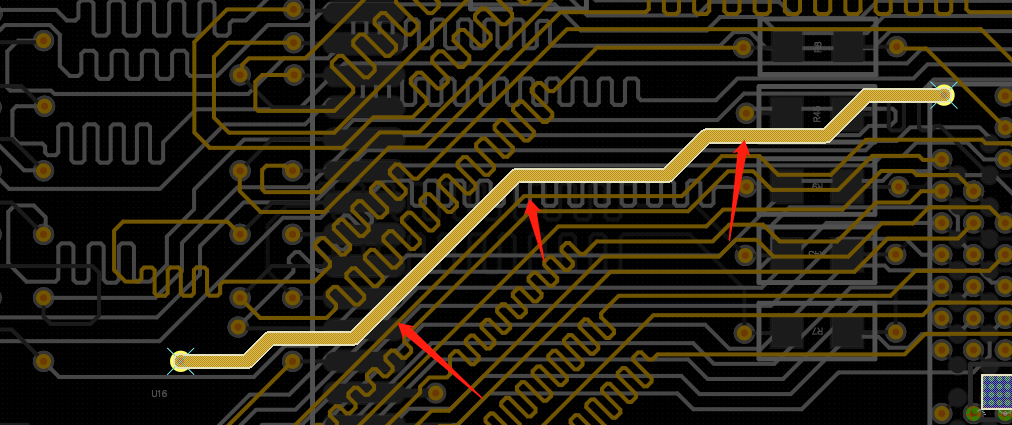

数据线与地址线之间的分割线上需要打地过孔,建议150mil一个第4层数据线和地址线之间也需要添加一根地线分开2.等长存在误差报错3.有器件连接的网络要创建Xsignals进行等长4.注意电源需要再电源层处理一下,铺铜进行连接5.注意器件不要

机壳地以及电源地没有正片铺铜处理也没有负片分割处理,注意地是需要处理的:变压器上除了差分信号,其他的加粗20MIL走线:电源层也并未处理电源 :TX RX信号之间用GND走线隔开:RX TX没有创建等长组进行等长:差分对内等长误差为5MIL

之前我们讲了PCB叠层7大设计技巧及注意事项方面,接下来我们将谈谈后面的知识点,希望对小伙伴们有所帮助,欲看前篇可点击右侧链接《PCB叠层怎么搞?这篇文一次性全告诉你!(上)》。8、控制信号和电源层的间隔为了避免信号层和电源层之间的互相干扰

电源和地是高速PCB设计中的重要对象,它们的布局布线处理好坏直接决定着成品的性能运行和串扰大小,若是稍有不慎,很容易拖慢项目进度。所以下面讲讲电源和地的高速PCB布线处理方法,希望对小伙伴们有所帮助。第一,尽量给出单独的电源层和地层;即使要

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到八层板的叠层来进行示例讲解单面PCB板和双面PCB板的叠层对于两层

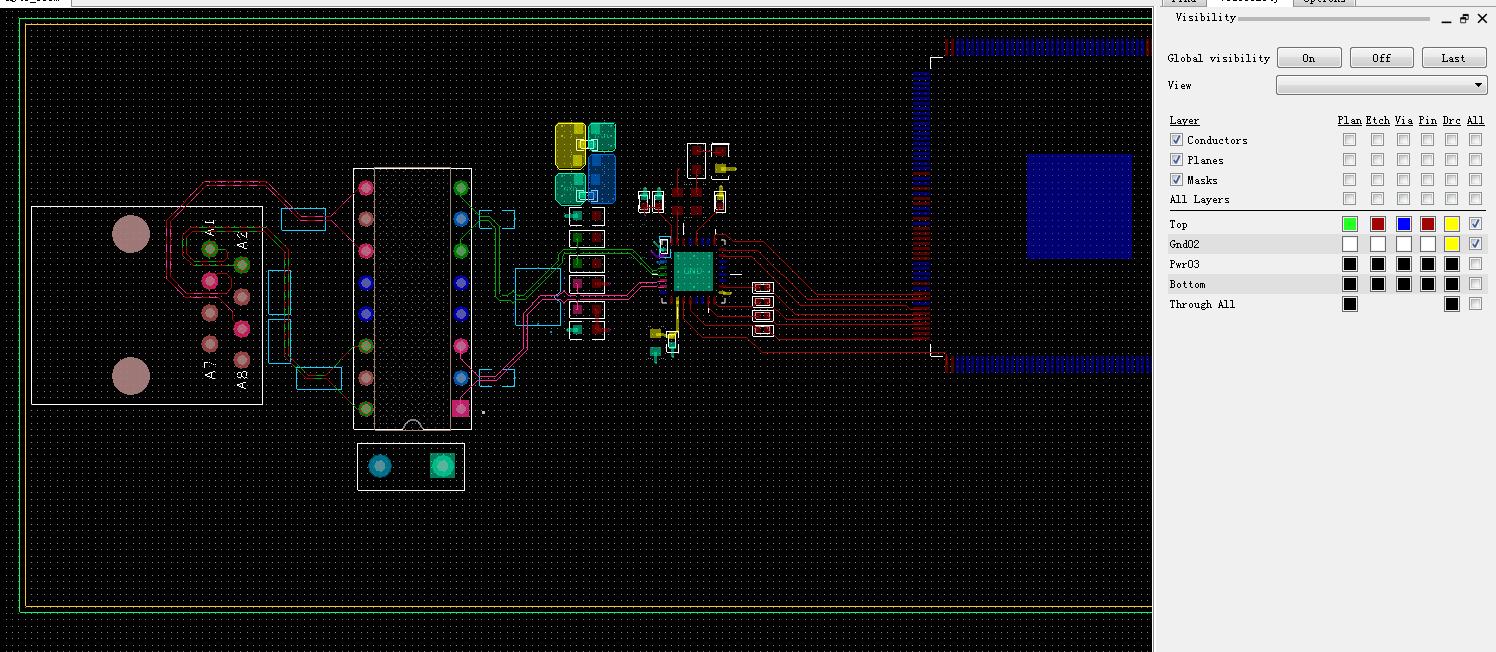

答:在做PCB设计过程中,叠层时可以选择是负片工艺还是正片工艺,如果层数较少,一般都可以正片处理,层数较多、数据量较大时会选择负片工艺对电源层进行处理。

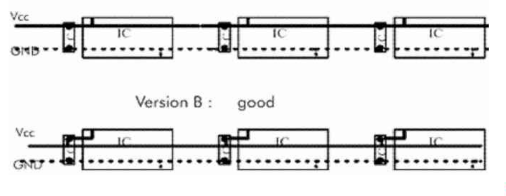

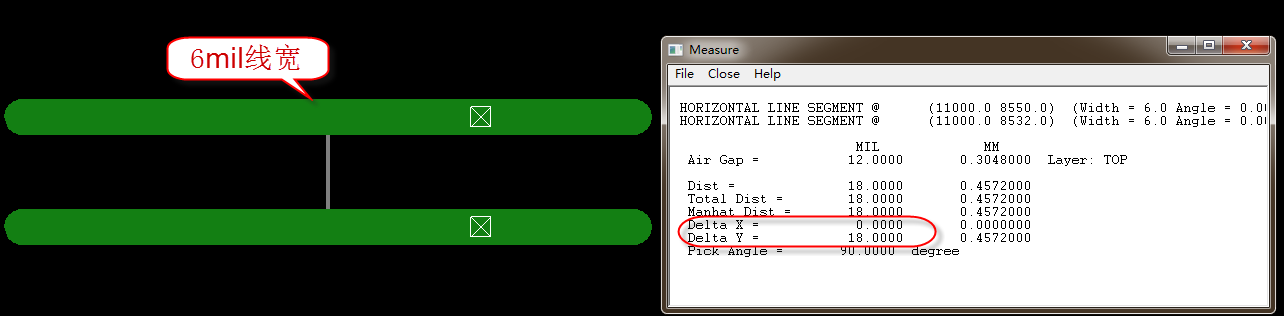

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

答:20H原则是指电源层相对地层内缩20H的距离,H表示电源层与地层的距离。当然也是为抑制边缘辐射效应。在板的边缘会向外辐射电磁干扰。将电源层内缩,使得电场只在接地层的范围内传导,有效的提高了EMC。若内缩20H则可以将70%的电场限制在接地边沿内;内缩100H则可以将98%的电场限制在内。我们要求地平面大于电源或信号层,这样有利于防止对外辐射干扰和屏蔽外界对自身的干扰,一般情况下在PCB设计的时候把电源层比地层内缩1mm基本上就可以满足20H的原则。

扫码关注

扫码关注