- 全部

- 默认排序

在电子系统中,晶振作为关键的时钟源,备受电子工程师的关注,然而在设计过程中,很容易听见这样的说法,如:晶振精度不准,容易导致电路稳定差,这种说法是否属实?下面一起来看看吧!1、晶振精度对系统稳定性的影响晶振的精度将直接影响到系统时钟信号的准

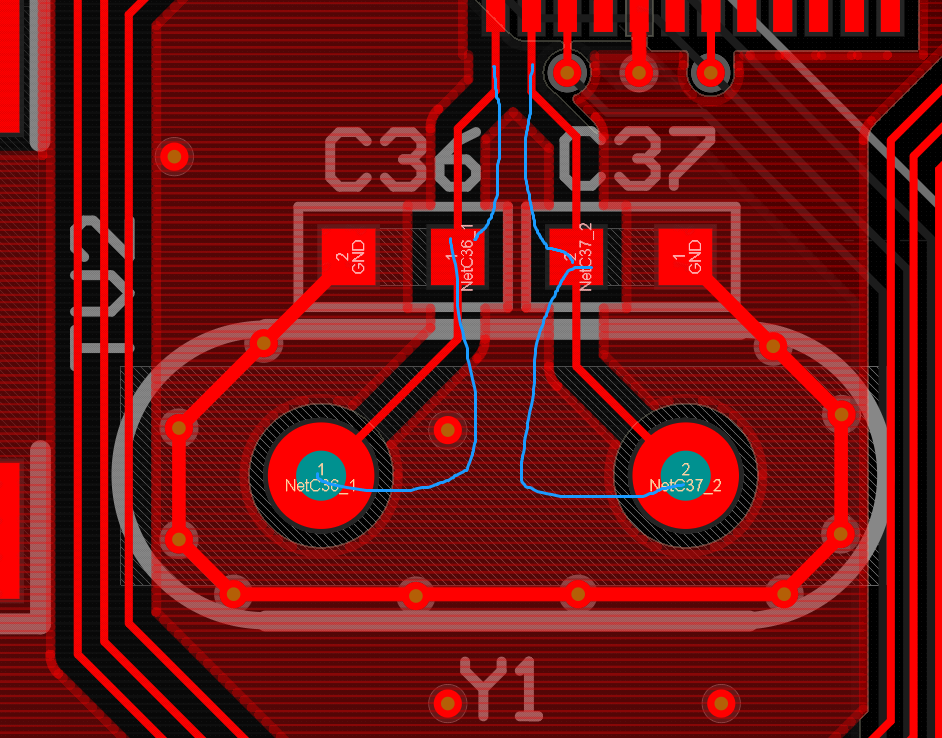

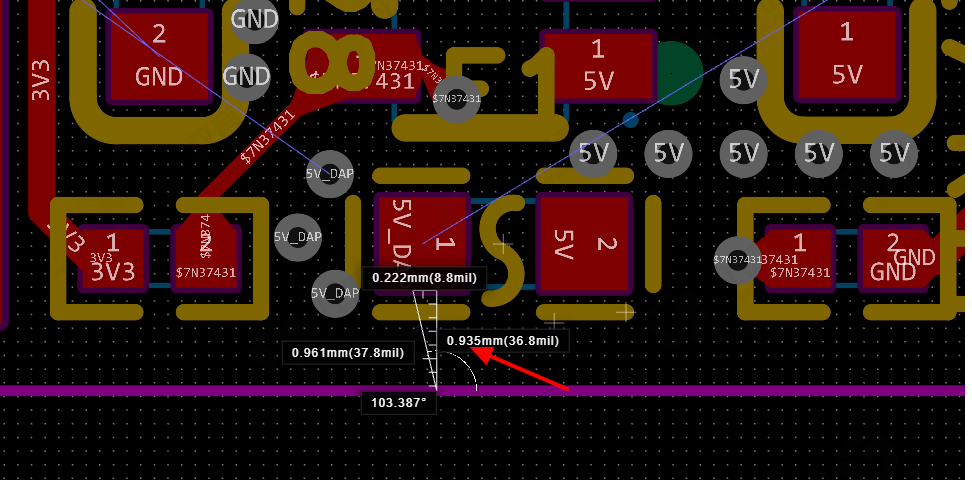

晶振走内差分需要再优化一下2.地分割间距最少1mm,建议2mm,有器件的地方可以不满足3.反馈信号走线需要加粗4.电感中间挖空就不要有铜皮5.输出打孔要打在电容后面6.注意过孔尽量盖油,不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特

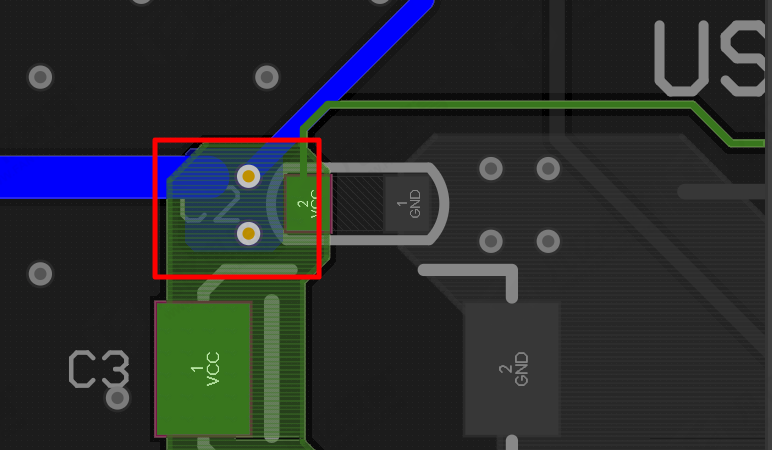

1.电源输入应该多打过孔加大载流2.差分布线避免直角,换层应靠近打一对回流地过孔3.晶振需要包地处理4.232C+C-,V+V-所接电容需要加粗走线

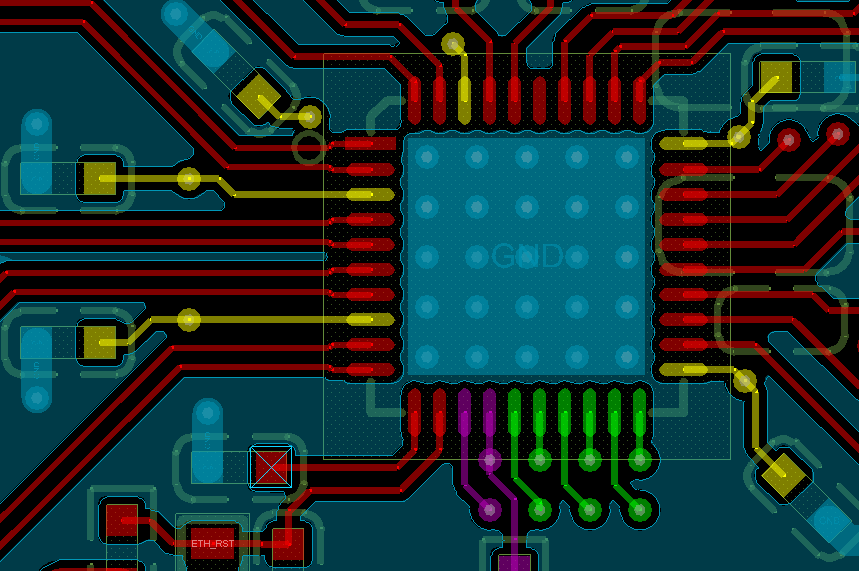

此处电源走线要注意满足载流2.晶振需要走内差分,并包地处理3.器件摆放不要挡住一脚标识4.注意等长线之间需要满足3W5.注意电源要满足载流6.变压器要所有层挖空处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

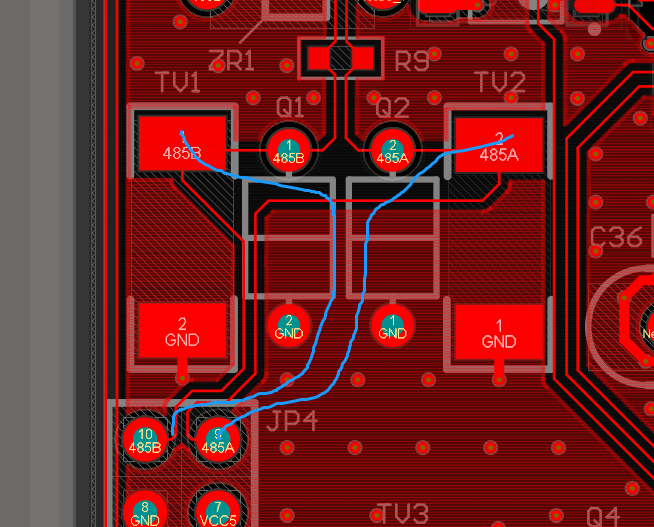

1.485需要走内差分处理2.跨接器件旁边尽量多打地过孔,间距建议2mm3.晶振下面尽量不要走线4.差分走线不满足间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

梁山派pcb设计特训营作业评审要求器件离板边5mm不要布局器件,除非特殊要求或后续板子设计可以添加工艺边。 【问题改善建议】:在贴片时留给设备的传送带固定用,建议无特殊要求板边5mm不要布局器件。2.晶振布局、布线错误。 【问题改善

扫码关注

扫码关注