- 全部

- 默认排序

随着集成电路技术沿摩尔定律发展至今,从第一代插孔元件、第二代表面贴装、第三代面积阵列,再到现在的芯片封装,这些封装技术以系统级封装技术(SIP)的实现奠定了基础,然而很少工程师知道,良好的SIP可明显改善电磁兼容和信号完整性问题。所谓的系统

有时候器件是“寿终正寝”,有时候是存在压力但不明显。器件的“寿终正寝”是一种源于物理或化学变化的累积性衰退效应。大家都知道,电解电容和某些类型的薄膜电容“终有一死”,原因是在微量杂质(氧气等)和电压力的共同作用下,其电介质会发生化学反应。集成电路结构遵循摩尔定律,变得越来越小,正常工作温度下的掺杂物

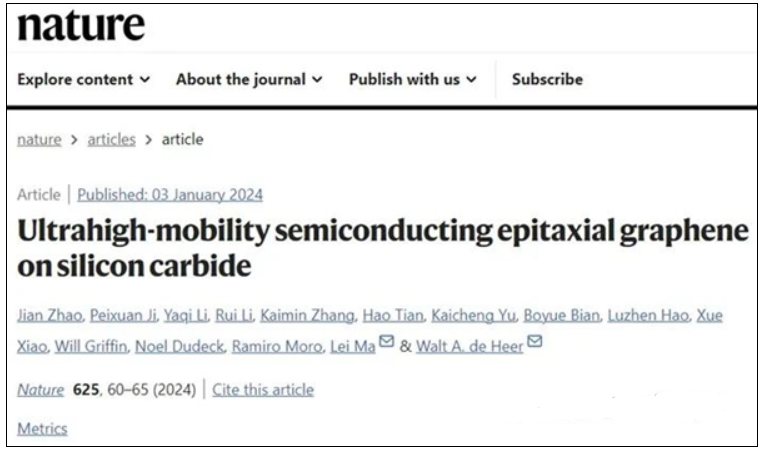

随着半导体芯片的制造即将达到摩尔定律的物理极限,很多公司及机构都在研究如何让半导体产生更加优秀的性能。在许多方案中,石墨烯备受关注。石墨烯(Graphene)是碳的同素异形体,碳原子以sp²杂化键合形成单层六边形蜂窝晶格石墨烯,只有一个原子

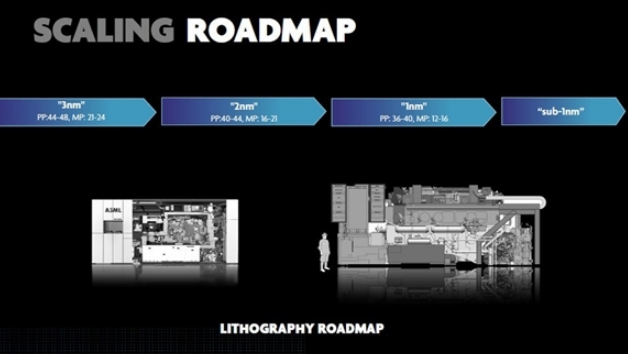

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

全球唯有台积电和三星能够制作5nm以下工艺的晶圆代工,然而随着芯片工艺制程的提升,研发难度越来越高,发布时间也越来越少,这也造成很多人说摩尔定律将死。纵观台积电的路线发展图,台积电将在2022年年底量产3nm工艺,2025年量产2nm,在此

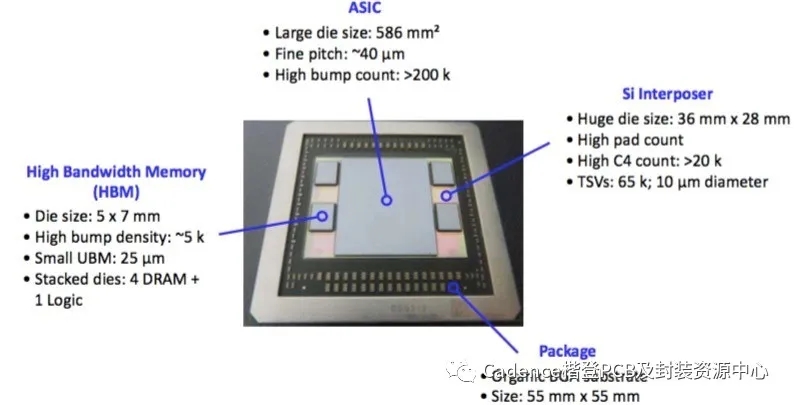

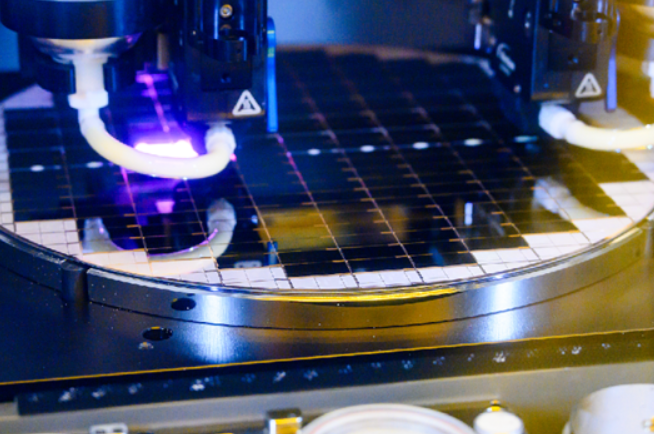

随着芯片产业的迅速发展,芯片间数据交换也在成倍增长,传统的芯片封装方式几不能满足巨大的数据处理需求。同时,随着芯片制造逐渐进入摩尔定律的无理极限,芯片制程工艺提升放缓,以3D堆叠封装为代表的先进封装技术即将成为未来的重要发展方向。以苹果为例

提起摩尔定律,很多人都不会陌生,英特尔创始人戈登·摩尔提出:“集成电路上可以容纳的晶体管数量,每经过18-24个月便会翻一番。”但随着芯片制程的提升,摩尔定律即将达到物理极限。据外媒报道,随着新工艺节点的不断推出,芯片制程工艺也正在向着物理

随着芯片产业迅速发展,芯片间数据交换也在成倍增长,传统的半导体封装已经无法满足巨大的数据处理需求。同时,芯片制造逐渐逼近摩尔定律的物理极限,芯片制程工艺提升放缓。在这个关键时期,3D、SIP等新型封装技术开始问世,由于封装技术在很大程度上影

在通信行业快速发展的今天,通信工程师作为行业的中坚力量,需要不断跟进技术的步伐,掌握行业发展的基本规律,本文将介绍十大定律,这些定律不仅揭示了通信行业的技术发展趋势,也为工程师在实际工作中提供了参考和指导。1、摩尔定律由英特尔公司的创始人之

自从芯片工艺已进行到3-5nm工艺制度,逐渐达到摩尔定律的物理极限,这也造成很多企业及专家唱衰摩尔定律,但作为摩尔定律的追随者,英特尔为此不断努力验证者摩尔定律的可行性。近日,英特尔正式宣布:已实现基于业界领先的半导体封装解决方案的大规模生

扫码关注

扫码关注