随着集成电路技术沿摩尔定律发展至今,从第一代插孔元件、第二代表面贴装、第三代面积阵列,再到现在的芯片封装,这些封装技术以系统级封装技术(SIP)的实现奠定了基础,然而很少工程师知道,良好的SIP可明显改善电磁兼容和信号完整性问题。

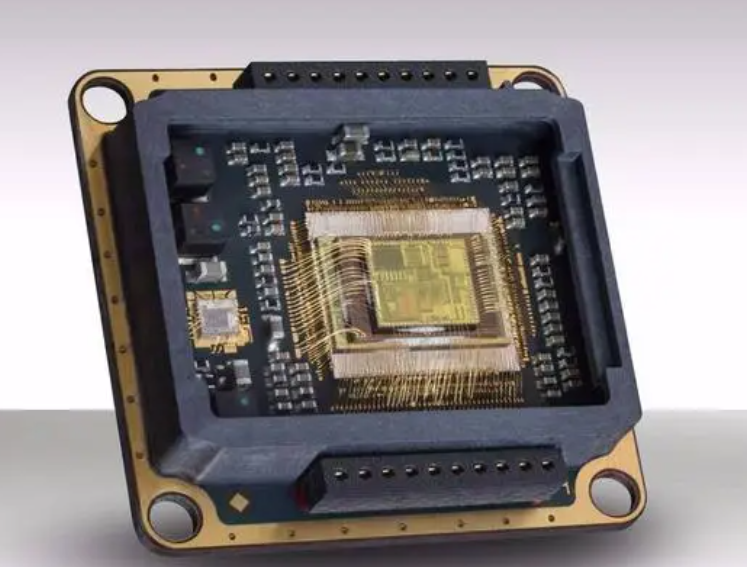

所谓的系统级封装,是指将多个具有不同功能的有源组件与无源组件,及诸如微机电系统(MEMS)、光学(Optics)元件等其他元件组合在同一封装中,成为可提供多种功能的单科标准封装组件,形成一个系统或子系统。

系统总线传输数据的带宽与时钟频率f、数据宽度W成正比,一般来说,当功能整合愈发复杂时,芯片尺寸相对来说会越大,造成内部信号线路在进行全局布线时路径太长,信号传递过久的情形,且容易产生电磁干扰现象。

与板级连线相比,SIP封装内裸片间的互连引线长度更短,这有效减少了系统的互连线延迟和串扰,降低了容抗,使器件能够工作在更高的工作频率,从而有效提高了带宽。

裸片间较短的互连还会带来一些潜在的好处:裸片的I/O输出不必采用强驱动设计,使用小功率的I/O缓冲器就可保证裸片间传输信号的完整性,因此可以采用更低的工作电压,从而进一步减小了器件的功耗。此外也可以减少为屏蔽高速信号管脚引起的寄生电容和寄生电感而引入的电源和接地引脚,减少了和PCB间的I/O管脚数量。

扫码关注

扫码关注