- 全部

- 默认排序

注意等长线之间需要满足3W规则2.VREF电源需要加粗到15mil以上3.等长超出误差值4.滤波电容尽量均匀摆放,确保一个管脚一个5.反馈需要加粗到10mil以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

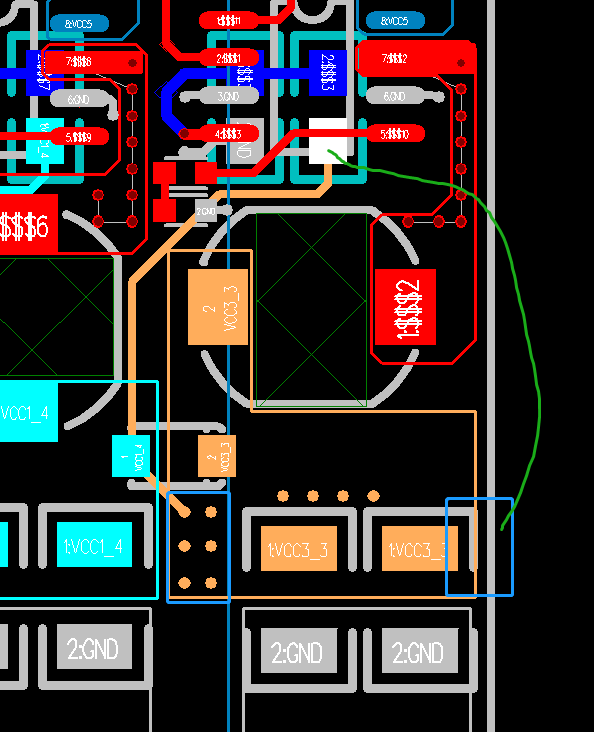

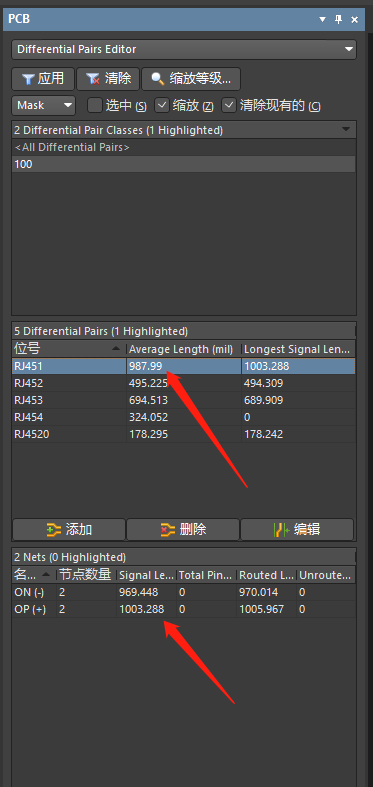

电源输出打孔要打在电容后面,反馈从最后一个电容后面取样2.差分出线要尽量耦合3.输入打孔要打在电容前面,先经过电容在进入管脚4.数据线需要满足3W规则,后期自己调整一下间距5.地址线也要满足3W6.电容尽量靠近管脚放置,以上评审报告来源于凡

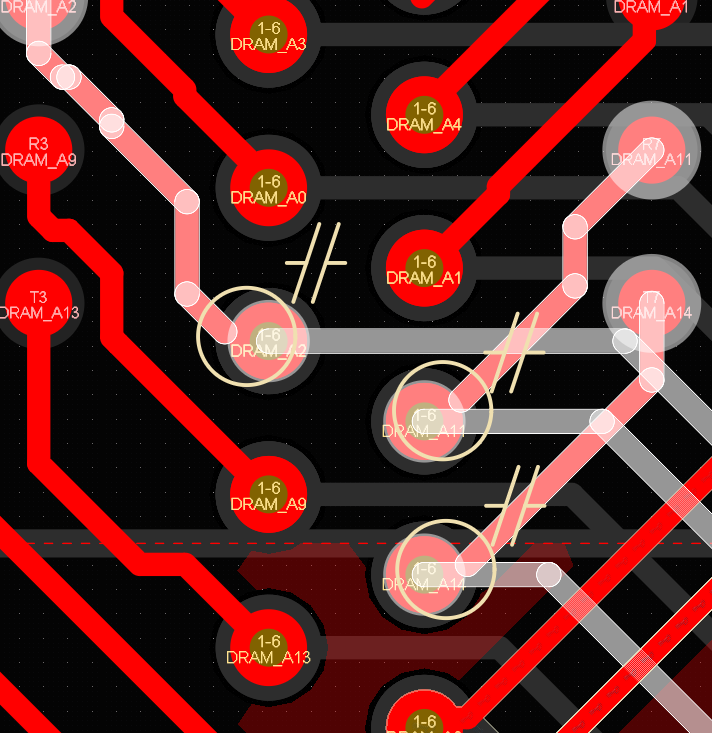

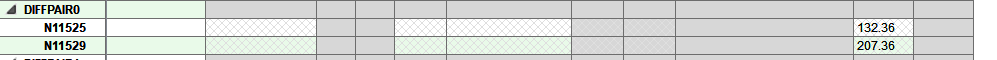

晶振需要走内差分处理2.SDRAM数据线低八位和高八位需要分开创建class,分别进行等长3.注意数据线之间等长需要满足3W规则4.地址线也需要满足3W规则5.滤波电容靠近管脚放置,尽量保证一个管脚一个6.数据线等长误差建议+-25,mil

注意低脂线等长需要满足3W2.数据线之间等长也需要满足3W3.电感所在层的内部需要挖空4.VREF的电源走线需要加粗到15mil以上5.电容摆放尽量保证一个管脚一个,靠近管脚放置6.除了散热过孔,其他的都可以盖油处理以上评审报告来源于凡亿教

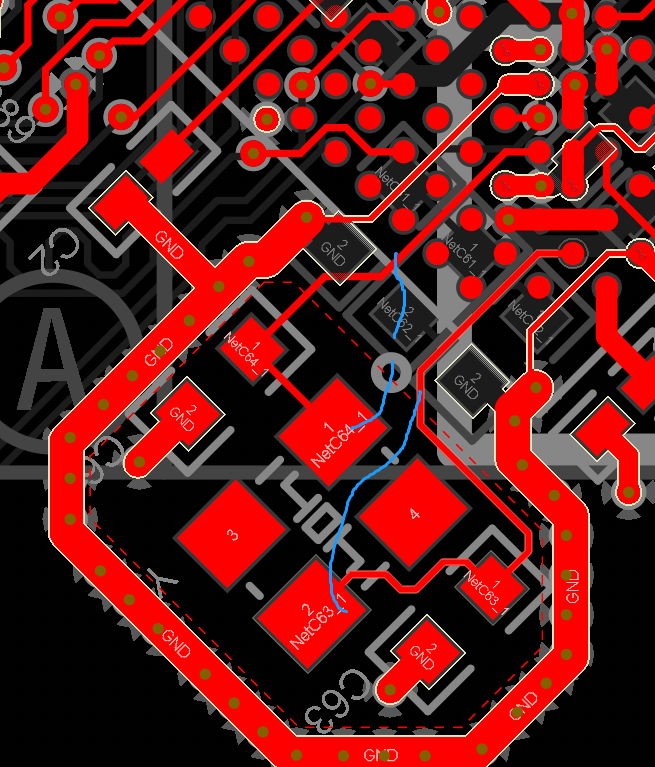

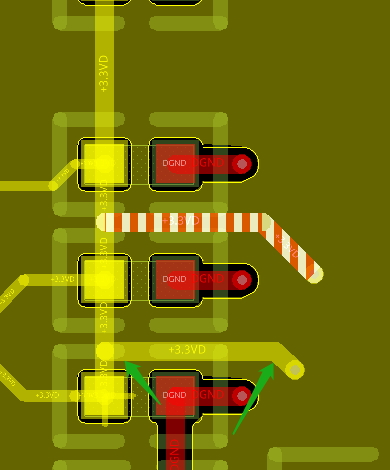

存在多出开路2.走线需要优化一下,尽量钝角3.此处铜皮出现载流瓶颈,后期自己把铜皮加宽一些4.存在多余的走线5.和孔需要优化一下,可以直接打孔,T点的臂可以不用满足3W6.注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特训班作

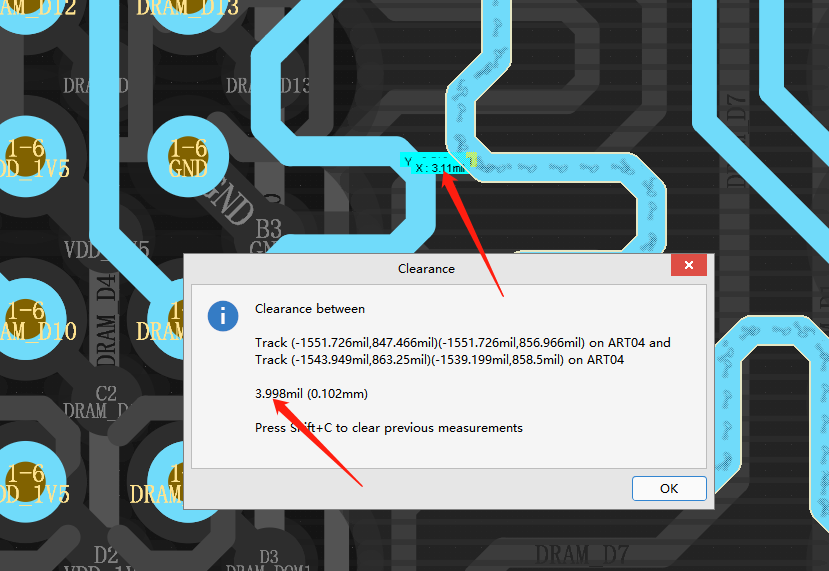

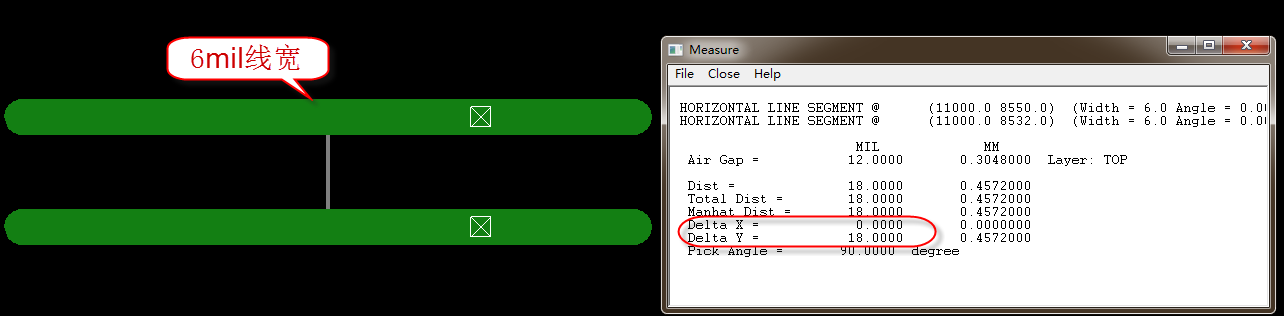

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

网口差分需要进行对内等长,误差5mil2.注意差分走线要注意耦合3.注意等长线之间需要满足3W规则4.等长存在误差报错5.地网络进行就近打孔,连接到地层,缩短回流路劲6.顶层BGA里面的铜尽量挖掉7.电感所在层内部需要挖空处理以上评审报告来

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注