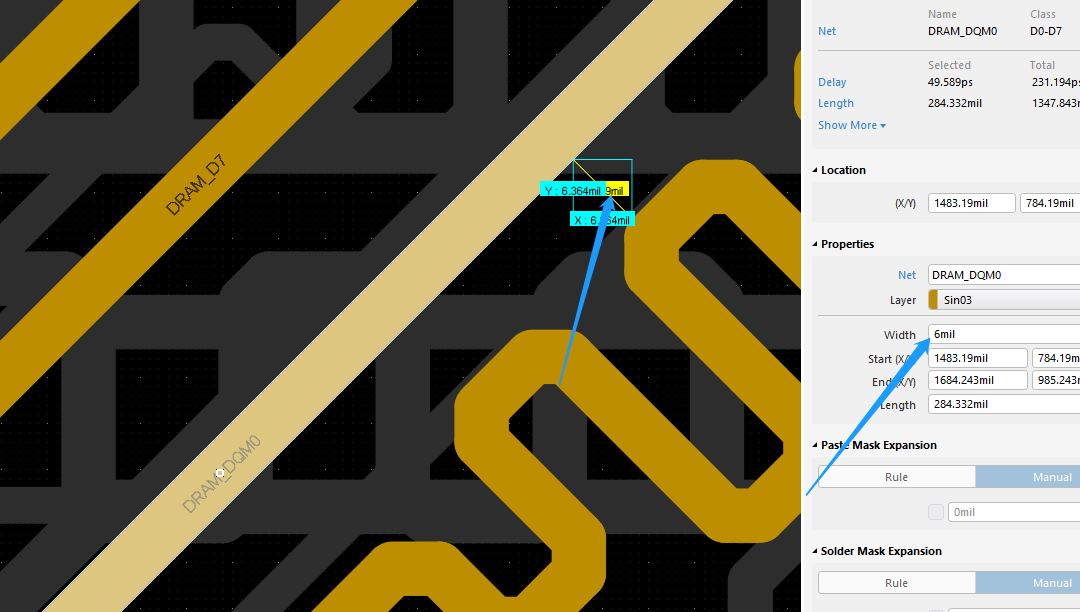

注意低脂线等长需要满足3W

2.数据线之间等长也需要满足3W

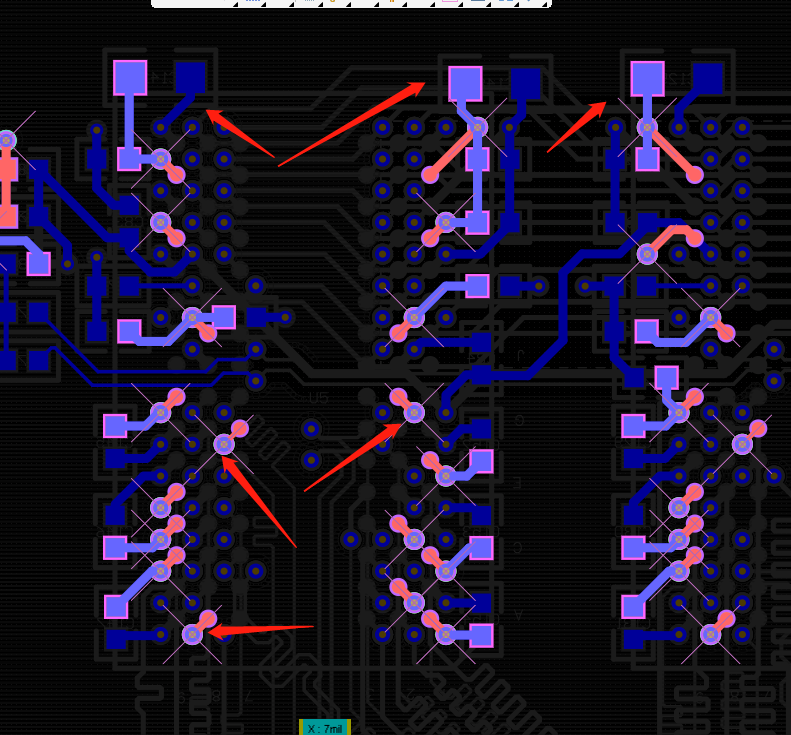

3.电感所在层的内部需要挖空

4.VREF的电源走线需要加粗到15mil以上

5.电容摆放尽量保证一个管脚一个,靠近管脚放置

6.除了散热过孔,其他的都可以盖油处理

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教:

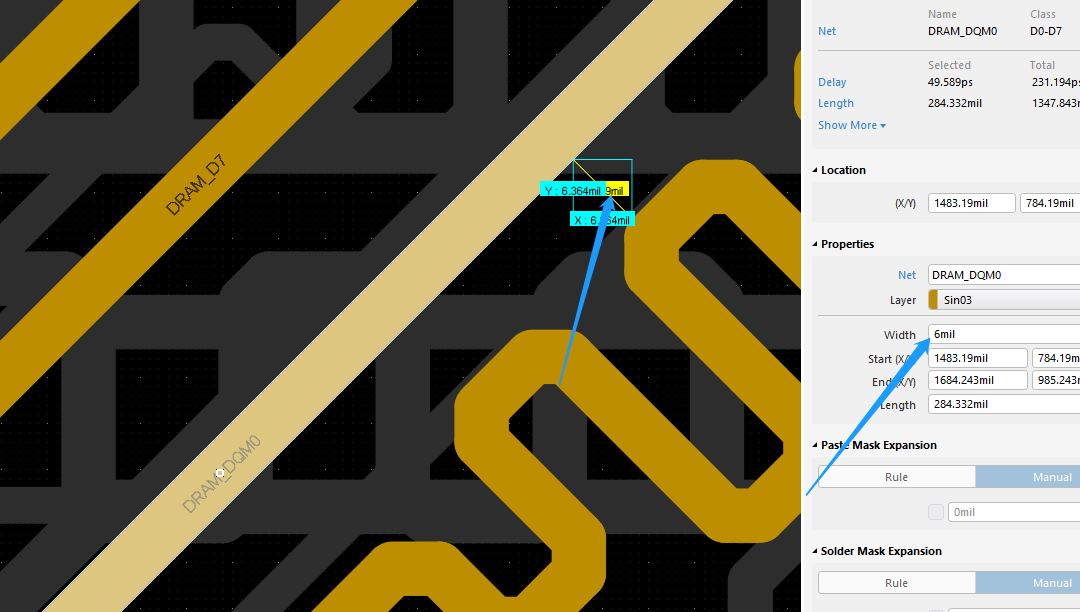

注意低脂线等长需要满足3W

2.数据线之间等长也需要满足3W

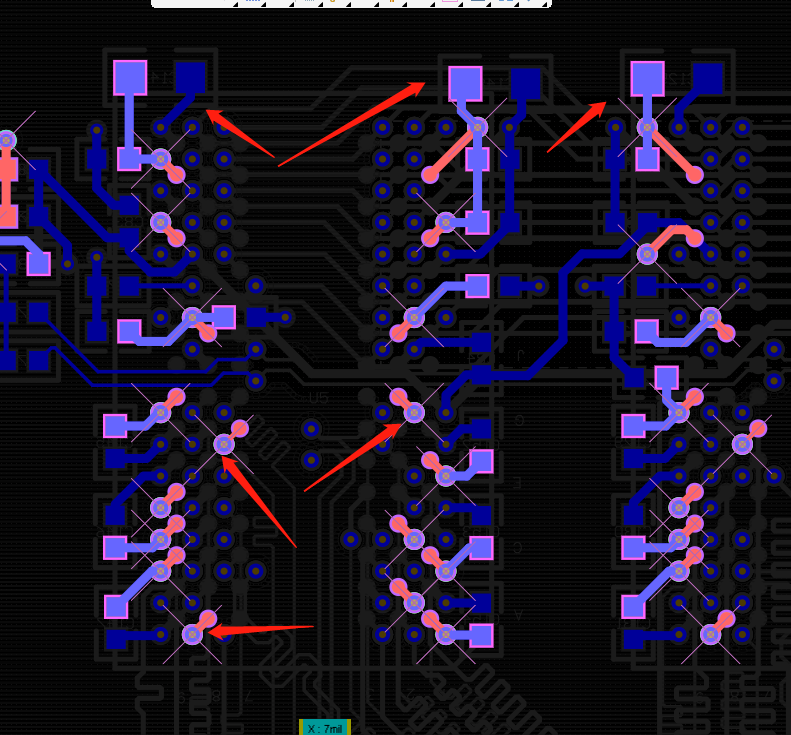

3.电感所在层的内部需要挖空

4.VREF的电源走线需要加粗到15mil以上

5.电容摆放尽量保证一个管脚一个,靠近管脚放置

6.除了散热过孔,其他的都可以盖油处理

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教: