- 全部

- 默认排序

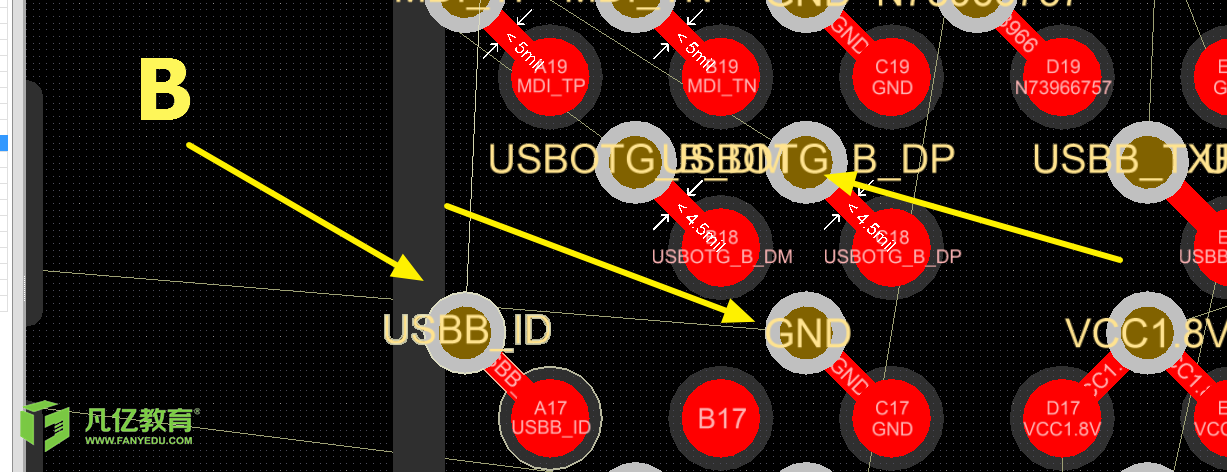

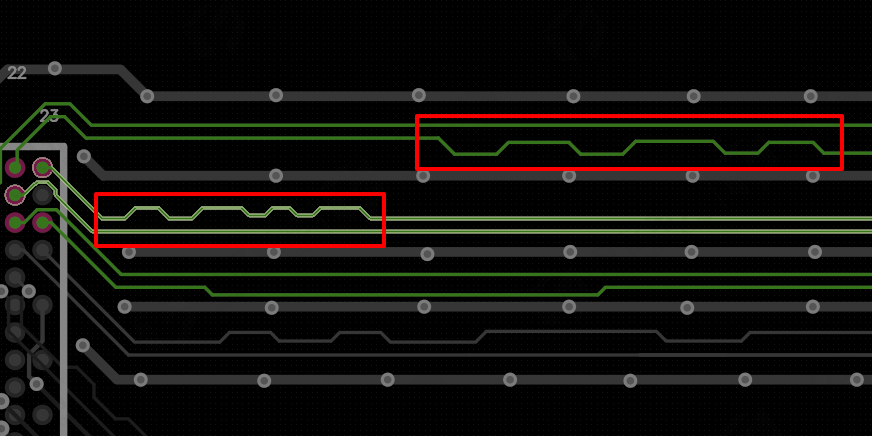

1.差分对内等长错误,按照规范图片要求等长2.单端控50欧姆差分控100欧姆阻抗,做四层板中间层为参考平面3.sclk不是差分信号,不要走差分布线,走单端线控50om4.差分出焊盘尽快耦合,用差分布线5.存在飞线没有连接6.差分组对间需要等

1.多处飞线没有处理2.差分对内等长绕线高度过高3.差分焊盘出线过长距离不耦合以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/ite

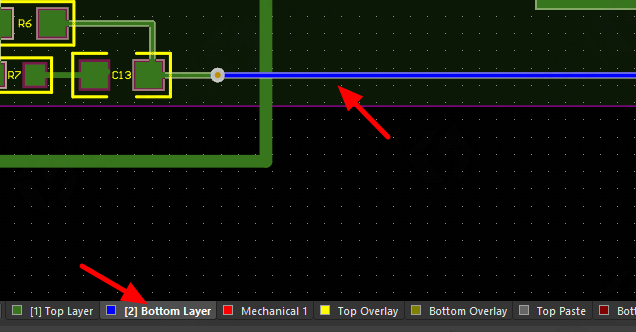

1.底层没有铺地铜,导致多处地网路飞线没处理2.多处铺铜没有网络,多处飞线没有连接3.dcdc需要单点接地,地网络没有打孔,应在芯片下方打孔和大地铜连接4.电源没有连接,多处过孔没有网络5.地网络没有连接,6.铺铜、走线避免直角锐角7.走线

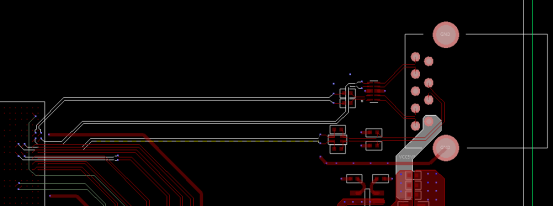

1.差分布线没有包地,需要每对差分单独包地打孔处理 2.差分换层旁边需要靠近打两个地过孔z3.差分布线长距离不耦合 4.差分没有等长,需要分组等长和对内等长处理 5.差分信号布线造成回路,应放置在后面尽量保持信号流向顺畅。 6. 存在飞线没

注意电源地跟机壳地之间满足至少2MM间距:器件注意放置完全,并且放置完成之后走线连接:把没有设计的器件布局布线设计下。变压器除了差分信号,其他信号也要走线连接完全:还存在多处飞线,存在信号没有连接完全:等长线之间需要满足3W间距:注意等长还

在规则里面这么多拓扑结构,很多时候我们只需要使用第一个shortest规则就可以,在ad中这几个出线规则其实并不需要我们去太多的纠结,因为对于器件而言不同的器件我们使用的布局方式又是不一样的,比如DDR什么时候用T点,什么时候用菊花链 ,什么时候用fly-By,等等这些,都是需要按照我们的行业规范进行布局和布线。

allegro pcb怎么显示网络线,显示飞线,或关闭网络线,显示部分网络线和全部网络线,或关闭部分网络线和都关闭全部网络。这就是这一次视频主要为大家讲解的内容。

扫码关注

扫码关注

![全能19期-allegro_THE的_第三次作业[2]千兆网卡PCB设计](https://api.fanyedu.com/uploads/ueditor/image/20230711/1689056641694508.png)