- 全部

- 默认排序

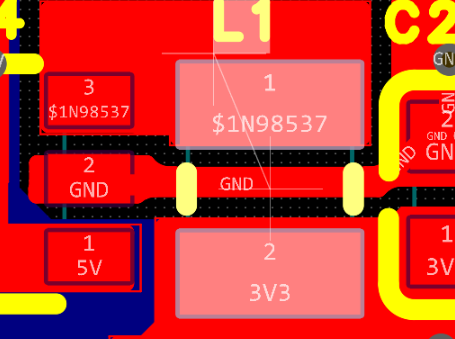

爬电间距与电气间隙的定义 u 电气间隙:可导电部件之间最最短的空间的距离。 u 爬电距离:可导电部件之间沿绝缘材料表面的最短距离。

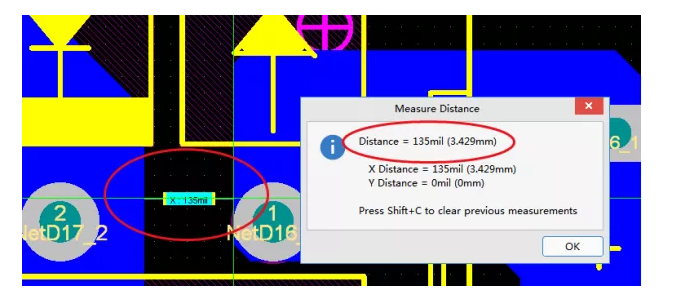

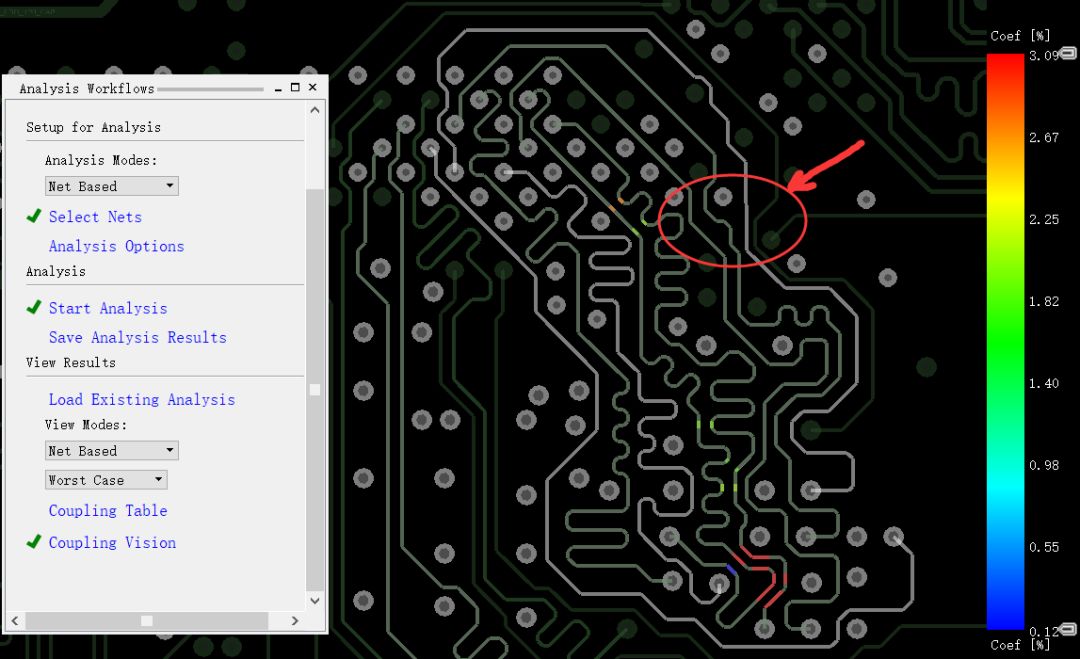

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

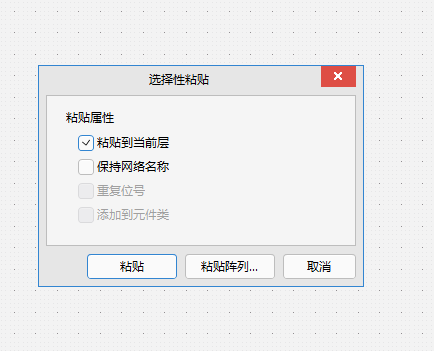

怎么样等间距的复制很多过孔?怎么带网络的复制走线?又或者是怎么样把元件的位号及网络从当前的这个PCB调用到另一个PCB板中呢?PCB设计当中经常会遇到这些问题,可以使用特殊粘贴也可以称为智能粘贴法来实现。

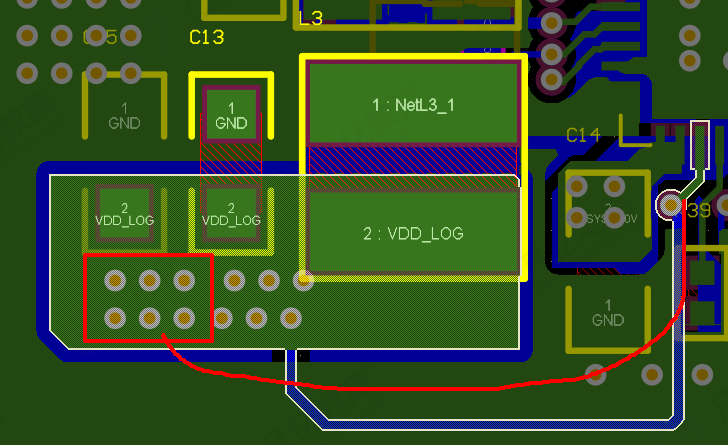

1.过孔应打到最后一个器件的后方,反馈信号需要连到最后一个电容。2.多处过孔上焊盘3.电源信号连接处铜皮需要加宽载流4.多处孤岛铜皮和尖岬铜皮5.注意保持过孔之间间距和过孔到焊盘间距不能太近6.电源信号走线需要加粗保持前后线宽一致7.走线不

跨接器件旁边尽量多打地过孔,间距最少1mm2.485需要走内差分处理,后期自己优化一下3.模拟信号需要加粗,单根包地处理4.差分线要尽量耦合,可以调整一下器件摆放的位置5.网口出差分信号外,其他的都需要加粗到20mil6.电感所在层的内部需

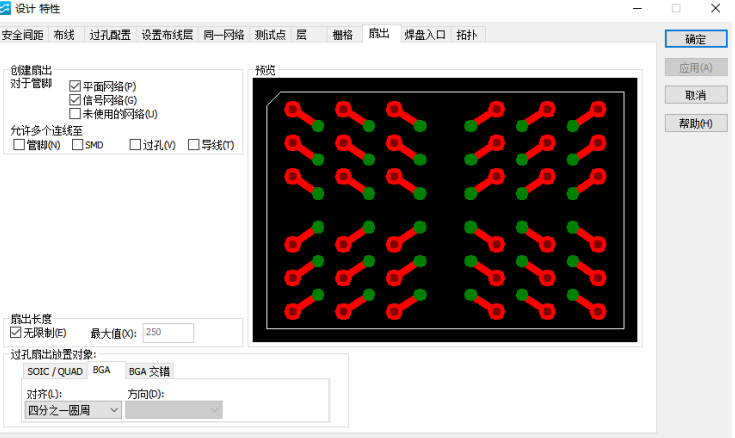

BGA扇出介绍

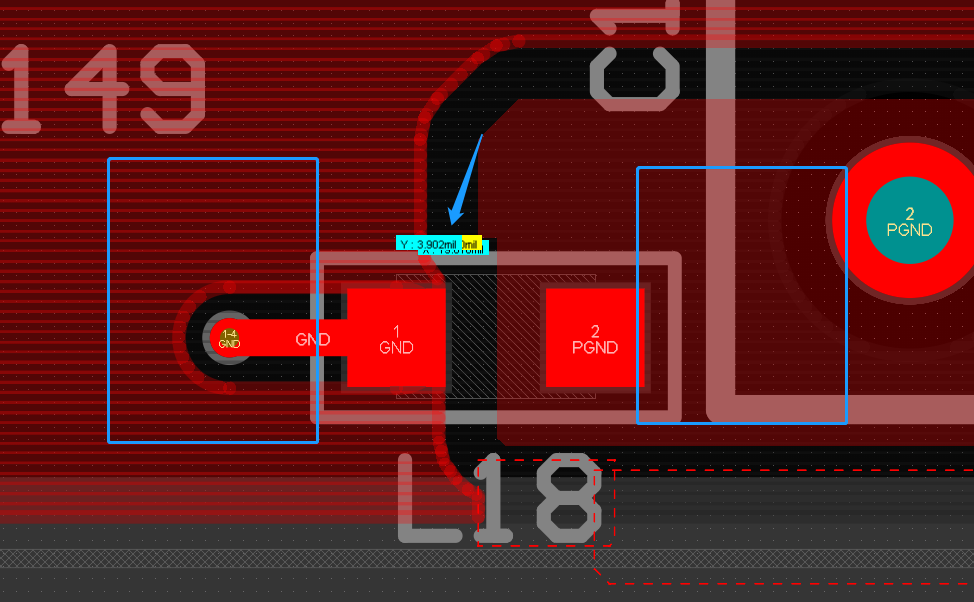

BGA扇出前须设置好规则,将BGA下方器件挪走,BGA下方所有层布线清除,若扇出时有DRC产生,会导致扇出失败。扇出前将格点设置为PIN间距的一半或者0,设置为PIN间距一半时须将精度设置好,否则会导到设置的格点4舍5入,设置失败。选择好合

一个完整的PCB封装是由许多不同元素组合而成的,不同的器件所需的组成元素也不同。一般来说,封装组成元素包含沉板开孔尺寸、尺寸标注、倒角尺寸、焊盘、阻焊、孔径、热风焊盘、反焊盘、引脚编号(Pin Number)、引脚间距、引脚跨距、丝印线、装

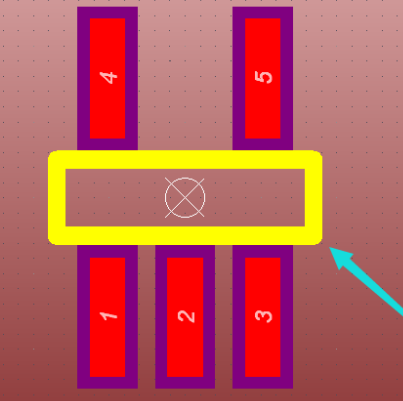

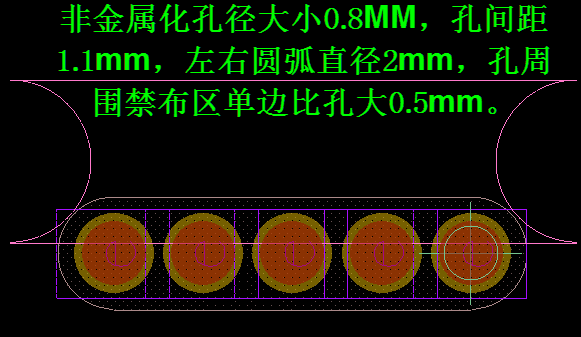

邮票孔设计尺寸一般可按此标准,邮票孔孔径大小0.8mm,为非金属化孔,孔与孔间距1.1mm或者1.25mm都可以,左右2个半圆弧直径尺寸2mm,有1/3孔径大小位置在分板处,一般邮票孔周围需要做禁布处理,以防止PCB板内走线、器件离邮票孔过近,禁布区域大小为单边比孔大0.5mm以上,如图4-118所示。

扫码关注

扫码关注