- 全部

- 默认排序

怎么样等间距的复制很多过孔?怎么带网络的复制走线?又或者是怎么样把元件的位号及网络从当前的这个PCB调用到另一个PCB板中呢?我们在进行PCB设计的时候,经常会遇到这些问题,所以足以表示了智能粘贴在我们进行PCB设计的重要性。因为以上的这些问题,都可以用智能粘贴去进行解决。

在pcb设计中,设置有原点,以便于进行精准的定位和测量,当想要任意的设置一个焊盘为中心原点时,该如何去进行操作,以便于更加方便的去定位那一个焊盘,视频有详细的讲解。

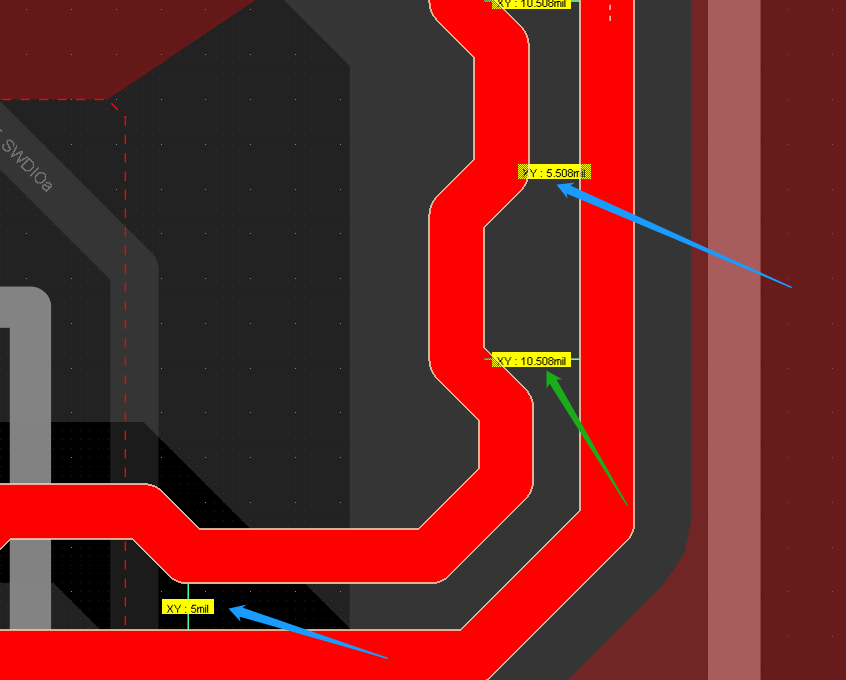

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

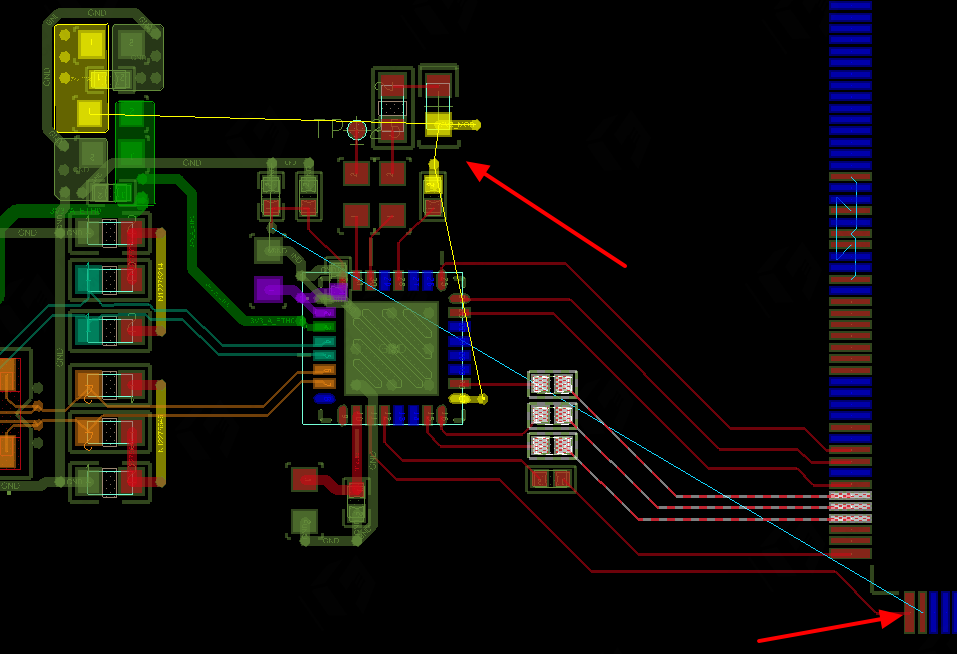

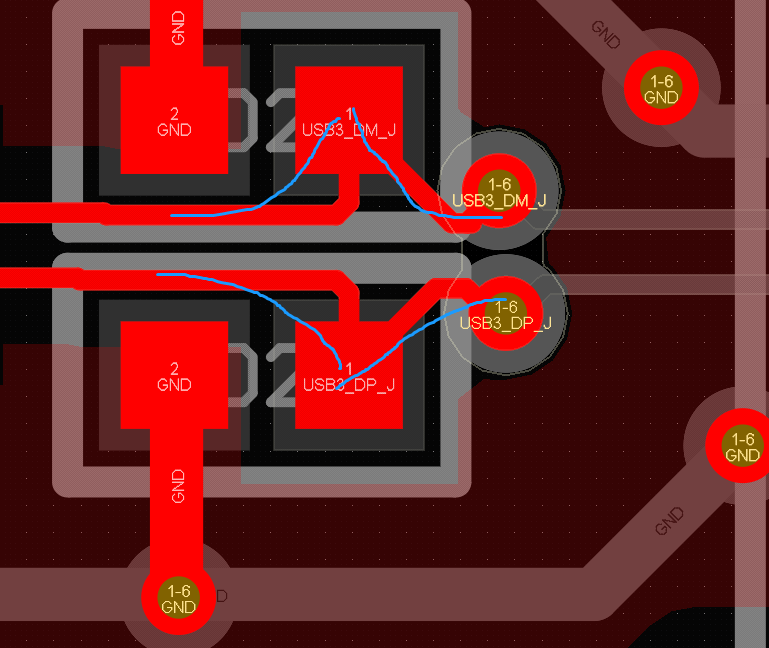

1.存在飞线没有链接,几处电源走线没连2.rx、tx两组差分对之间的间距至少4w以上3.差分没有对内,需要等长误差5mil。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:http

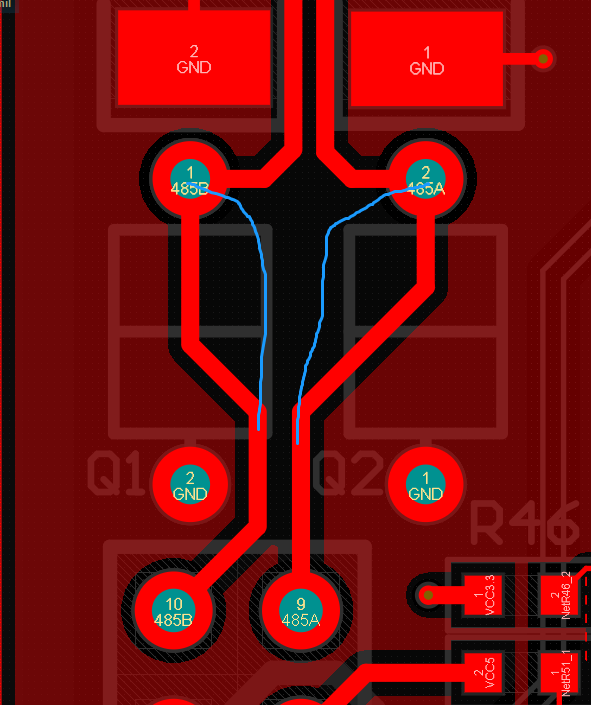

1.485需要走内差分2.网口除差分信号外,其他的都需要加粗到20mil3.差分对内等长5mil4.跨接器件 旁边尽量多打地过孔,分割间距尽量1mm以上5.模拟信号走线需要加粗6.电感所在层的内部需要挖空处理7.电源输入滤波电容法尽量靠近管

差分走线不满足差分间距要求,锯齿状等长也不能超过线距的两倍2.滤波电容和EAD器件靠近管脚放置3.输出打孔要打在最后一个滤波电容的后面4.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.此处走线不满足载流6.VBAT的滤

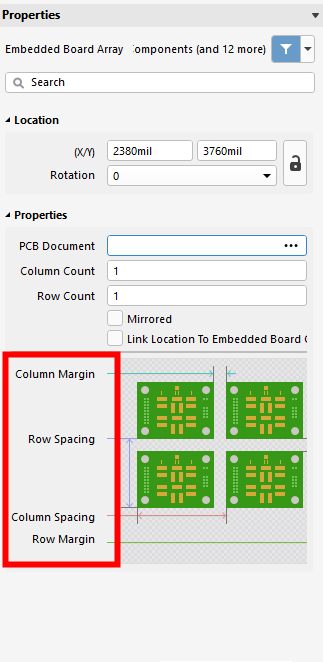

AD软件提供了一个非常方便且快捷的拼板功能,也就是拼板阵列功能,当执行这个功能之后,在其属性中是可以输入拼板之间的横向间距及纵向间距的相关参数,但是由于AD软件默认属性框大小的原因会导致无法找到输入相关参数的位置

规则(比赛要求):线宽要求10mil,引脚间距10mil。实际原件引角<10mil,怎么办是?通常是该线宽来实现连接还是改引脚间距规则。感谢回答

焊盘出现需要优化一下2.差分对内等长误差5mil3.其他没什么问题USB2.0注意差分走线要满足车分间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

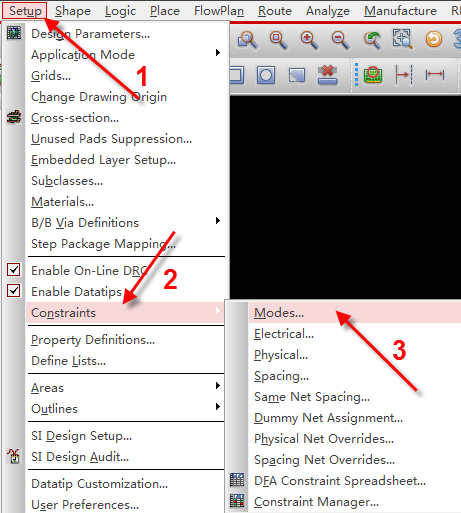

答:我们在前面的问答中讲述了走线的阻抗线宽以及不同的元素之间的间距规则之间的限定,但是,在Allegro软件中各个的约束规则需要在约束规则管理模式开启的情况下,才能起作用的。执行菜单命令Setup-Constrains,在下拉菜单中选择Modes,进行各个约束规则管理模式的选取,如图5-79所示:

扫码关注

扫码关注