- 全部

- 默认排序

在PCB设计中,可能会遇见各种计算现象,其中之一是需要快速地估计出印刷电路板上一根走线或一个平面的电阻值,而不是进行冗繁的计算。那么如何做?1、电阻的基本公式首先来了解下电阻的基本公式,从以下公式可知:电阻(R)与材料的电阻率(ρ)、长度(

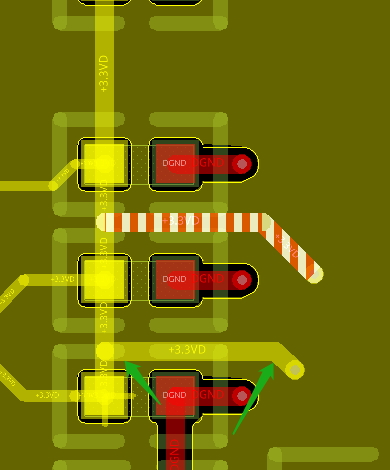

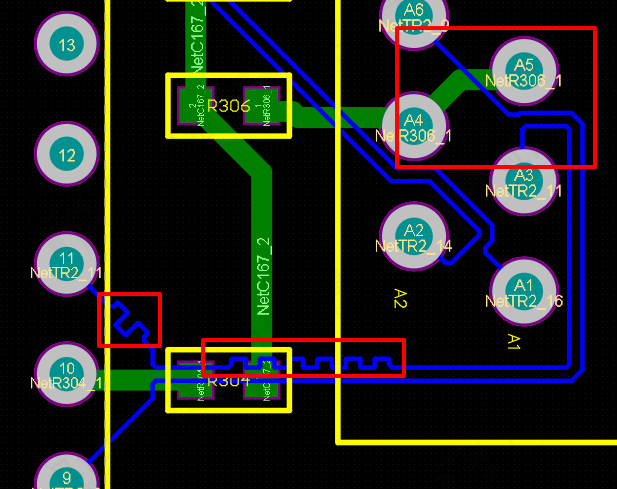

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

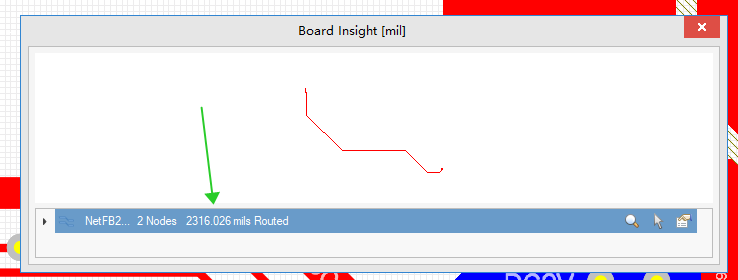

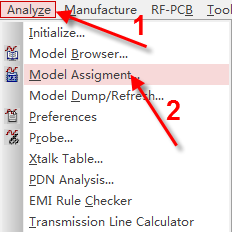

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

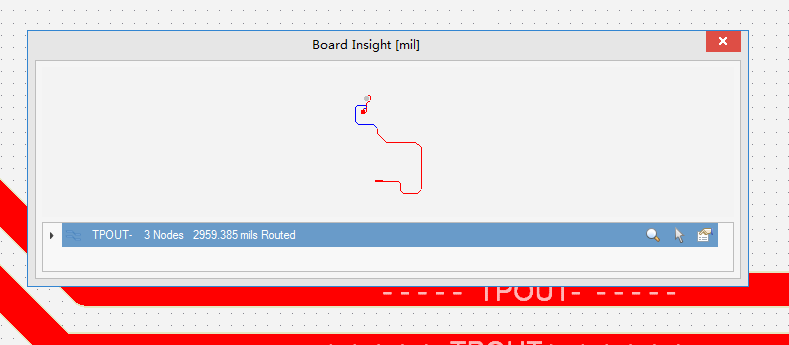

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

请问一下,AD20如何做等长啊 AD20和AD9.4这个显示功能显示好像有点区别AD20的Routed不显示线长,是因为我什么开关没打开吗?

无意间闯入了大神的论坛,感谢大神指导!目前跟随大神的脚步在学习AD,89C51开发板视频学习中,有2个疑问:1.尺子工具测完后会有长度标示类的文本(主要是AD17.1.5版本会出现,怎么进行相关设置)2.双层板走线换层这一块具体怎么用,百度了下按*号后层为单层模式,不知道怎么切换回所有顶底两层都显示

差分对内等长错误,应在引起不等长端绕线,绕线长度走线避免锐角同层链接多余打孔焊盘不完全连接,应连接到焊盘中间焊盘出线应避免从四角出线、在焊盘内拐弯以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

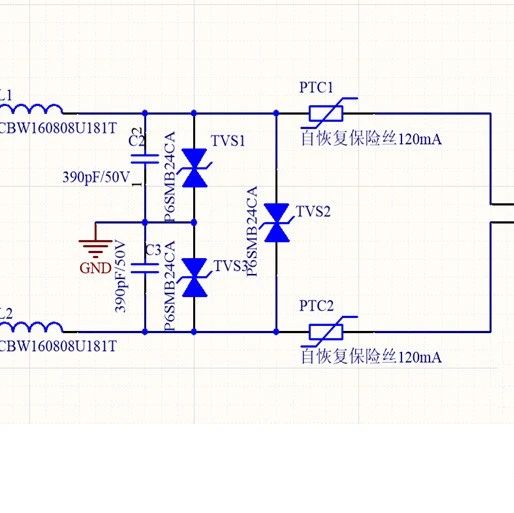

RS485电路原理图设计

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

扫码关注

扫码关注