- 全部

- 默认排序

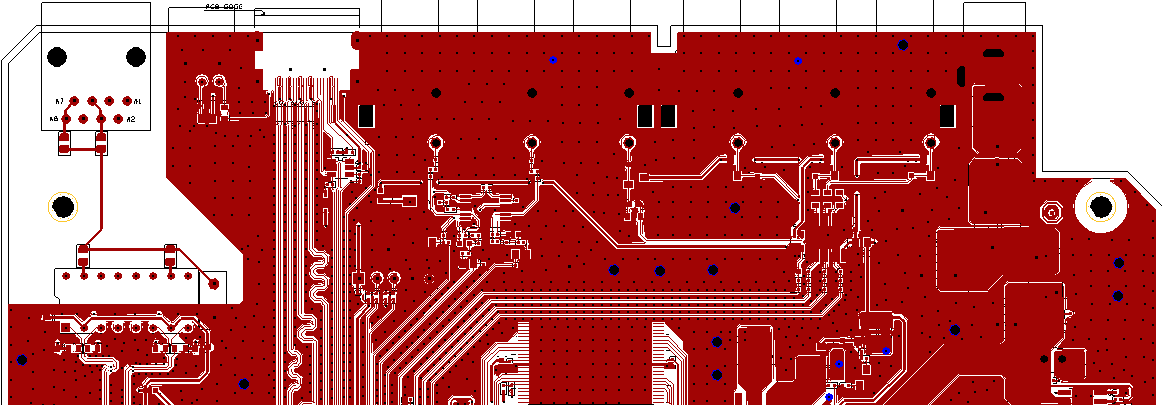

答:我们在使用Allegro软件进行PCB设计时,铺的铜皮都是动态或者是静态的铜皮,当打开Etch的时候,所有的走线跟铜皮都是同时显示的,如图5-130所示,在Allegro软件中是否可以隐藏铜皮呢,只显示走线呢,答案是可以的,具体操作如下:

直插器件必须用热风焊盘,这个说法对吗?如果不做成热风焊盘,就是铜皮不能是十字花连接,是全部连接了,电气性能不影响,只是以后拆除器件不方便,对吗?

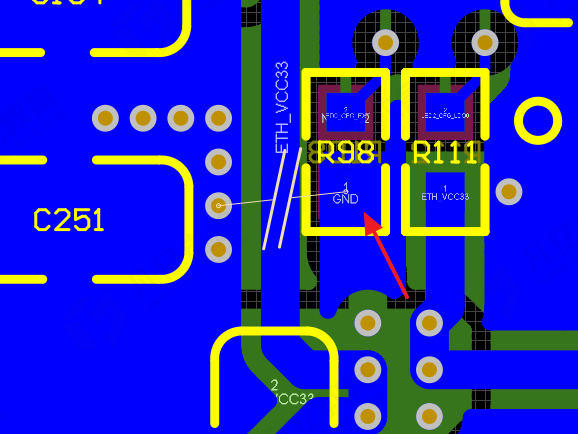

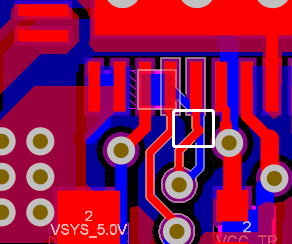

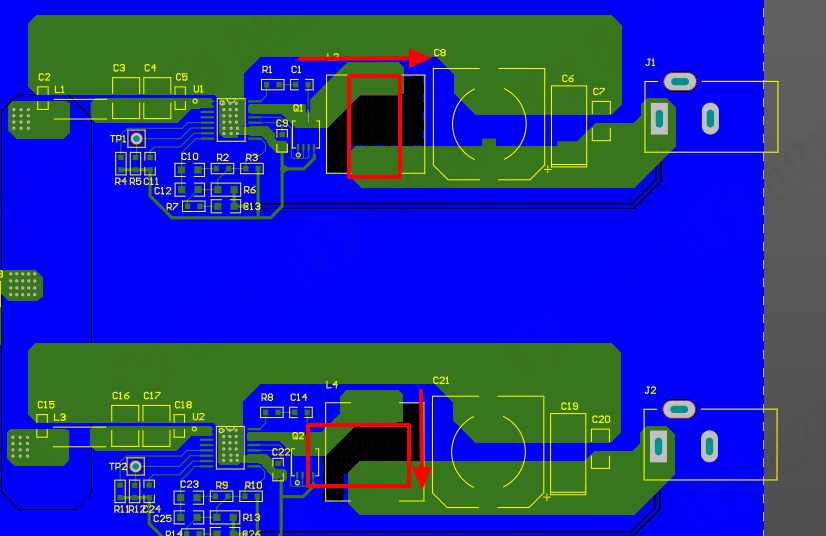

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

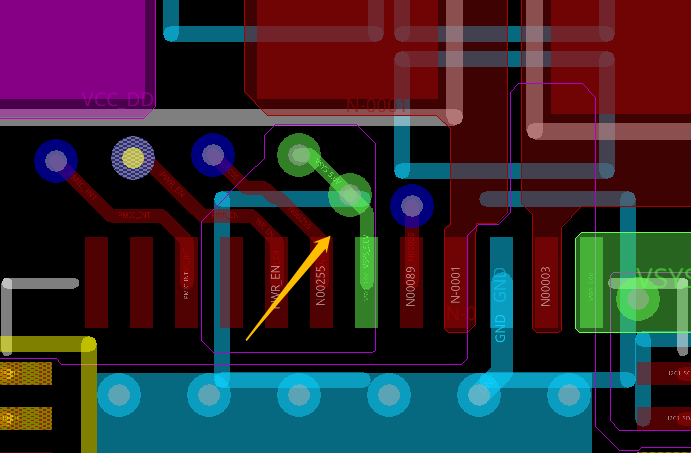

1,焊盘有开路。2.pcb存在drc4.多处孤岛铜皮和尖岬铜皮4.走线保持3w间距4.走线避免锐角5.差分换层旁边要打地过孔6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图8.同层连接不需要打孔9.时钟线要

这里走线和铜皮规范一下不要有直角锐角电感所在层铜皮要挖空电感下面不要走线这里铜皮太窄了,不满足载流以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taob

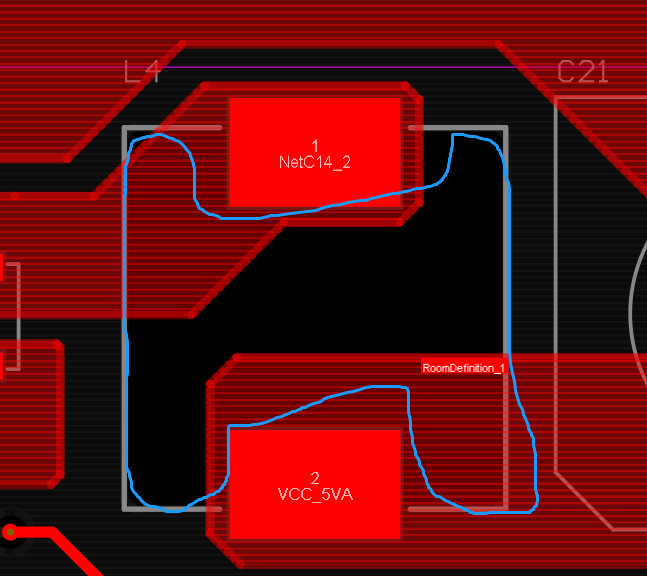

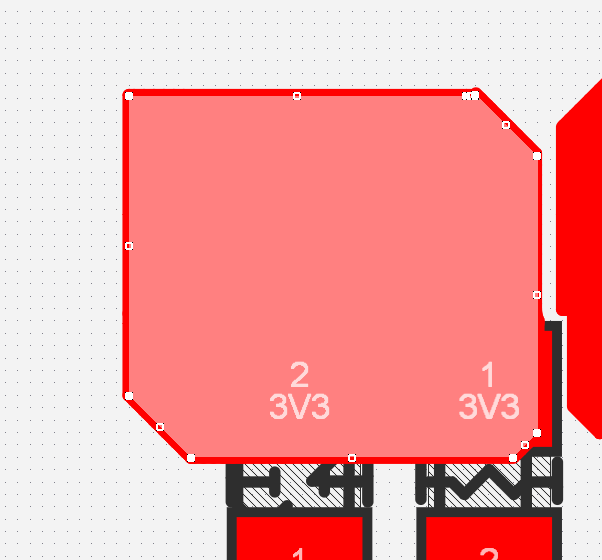

电感所在层的中间需要挖空处理2.反馈线走10mil即可3.过孔需要开窗处理,然后底层需要开窗进行扇热4.注意铜皮需要优化一下5.相同网络的铜皮和走线没有连接上,后期自己更改一下铜皮属性设置以上评审报告来源于凡亿教育90天高速PCB特训班作业

1.相邻电感应朝不同方向放置,不能同方向布局2.走线和铜皮没有连接,3.走线应从焊盘中间出线。4.电感挖空铺铜应该挖空整个丝印位置内部。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

扫码关注

扫码关注