- 全部

- 默认排序

2层stm32开发板评审

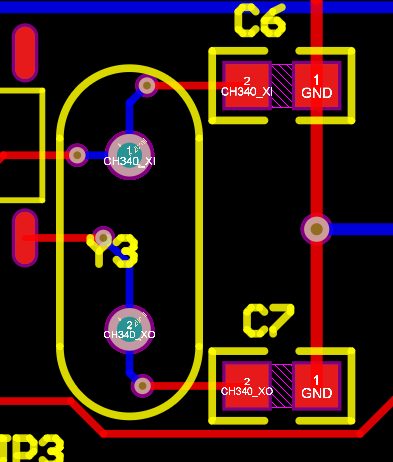

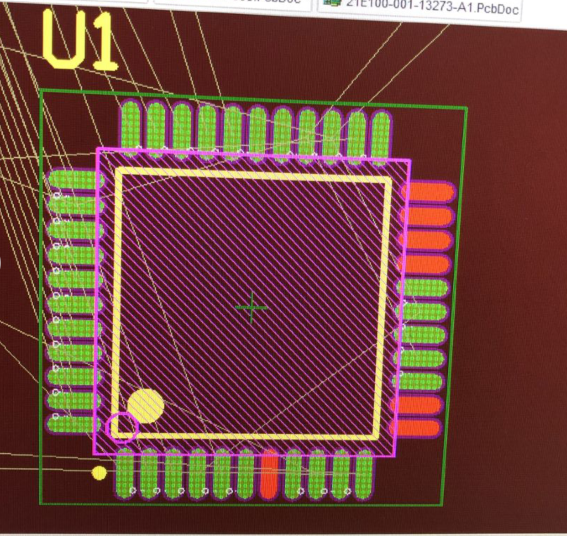

晶振这里不用打过孔进行换层,晶振要包地处理并打地过孔晶振的走线要类差分走线走线不要从焊盘中间出现容易造成虚焊。确认电源部分的走线是否满足载流要求485的信号走线100R差分或者走加粗类差分处理232这里所接的电容属于升压电容走线需要加粗处理

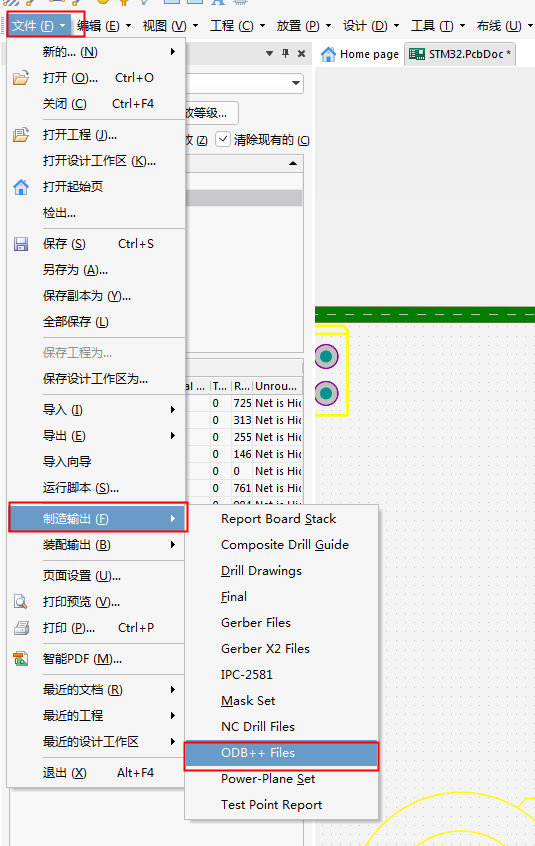

ODB++文件是由VALOR(IPC会员单位)提出的一种ASCII码,双向传输文件。文件集成了所有PCB和线路板装配功能性描述。涵盖了PCB设计、制造和装配方面的要求。包括所有PCB绘图、布线层、布线图、焊盘堆叠、夹具等所有信息。它的提出用来代替GEBER文件的不足,包含有更多的制造、装配信息。

FanySkill集成了使用Allegro软件进行PCB设计时辅助设计人员提高工作效率的20多个Skill功能。包含了封装制作、PCB布局、PCB布线等PCB设计过程中大概率会使用到的功能。Skill大部分内容为网友共享的开源内容或共享的加密Skill,本工具的源码内容完全开放给广大使用者,可方便使用者进行Skill内容学习和Skill工具自主订制,学习者不仅可使用本 工具提高自身工作效率,亦可以DIY一套自己的Skill工具。

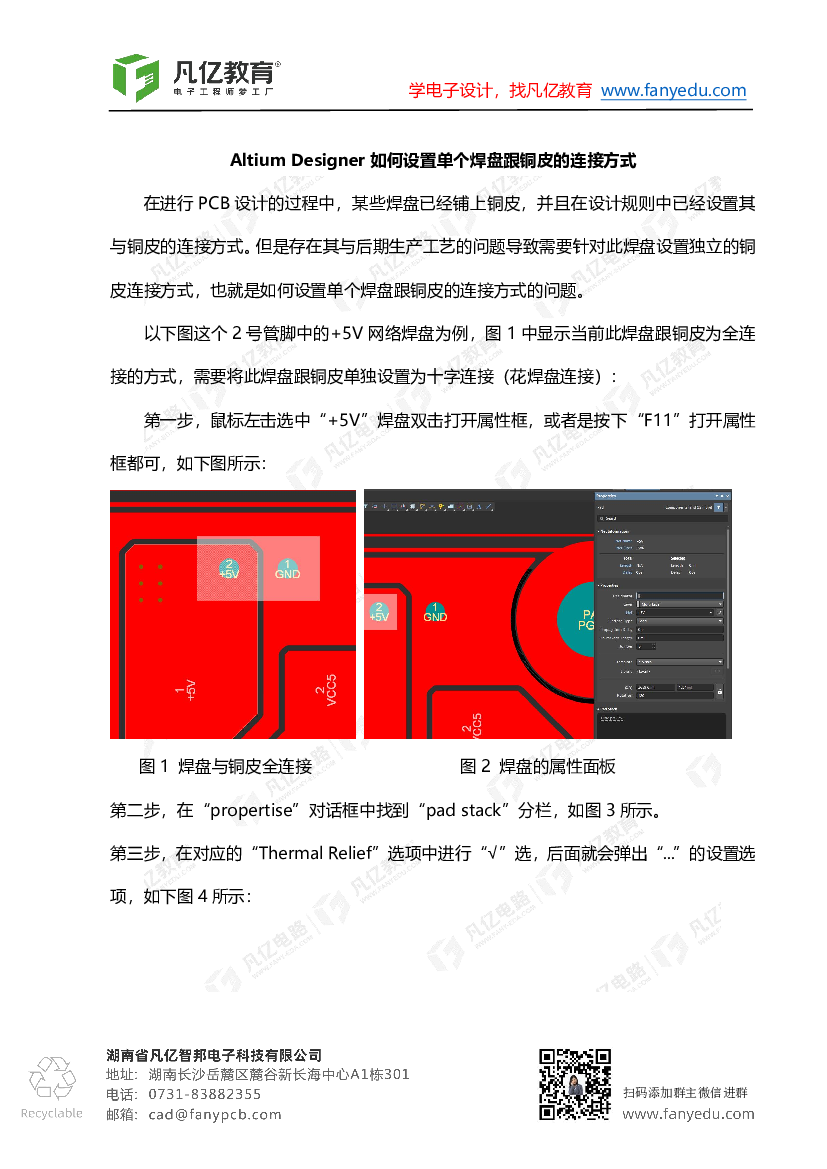

此处已经铺铜就不用再走线连接:电感内部的当前层挖空处理:其他的也一样,自己去修改。器件就近放,不要路径那么长:此处一个孔是否满足载流,可以多打一个:都看下LDO电路的信号线宽是否满足载流,不满足的出焊盘之后加粗宽度:这边也一致:其他的没什么

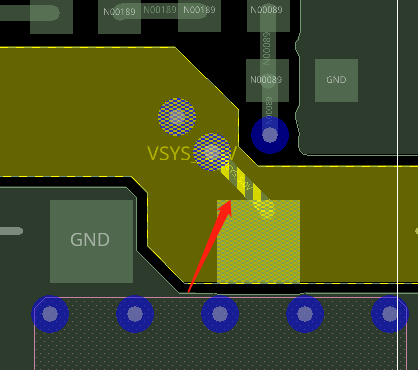

1.电源输入电路铺铜最窄处65mil铜宽中间级孔35mil,实际载流30mil自行判断载流是否足够2.走线多处锐角3.多处焊盘、走线不完全连接4.常规pcb尽量避免任意角度布线、铺铜5.从焊盘中心出线,出焊盘后再拐弯;45度角拉直,尽量避免

全站最新内容推荐

- 1AD-全能20期-SMT32-两层板-20期-杨文越

- 290天全能特训班22期-莱布尼兹的手稿 第十九次作业 SDRAM

- 3飞龙套餐allegro篇(PCB、硬件、EMC、单片机)

- 4飞龙套餐Altium Designer篇(PCB、硬件、EMC、单片机)

- 5飞龙套餐PADS篇(PCB、硬件、EMC、单片机)

- 6AD-全能21期-DM642开发板第一次作业

- 72024年中国及31省市3D打印市场分析及国家政策汇总

- 8AD- 杨皓文 第七次作业 2片SDRAM设计(菊花链)

- 990天全能特训班22期AD-沸点-2SDRAM

- 102.4GHz/6GHz Wi-Fi 带通滤波器: ACPF-7A24-TR1、ACPF-W065-TR1 产品介绍、特征及应用

扫码关注

扫码关注