- 全部

- 默认排序

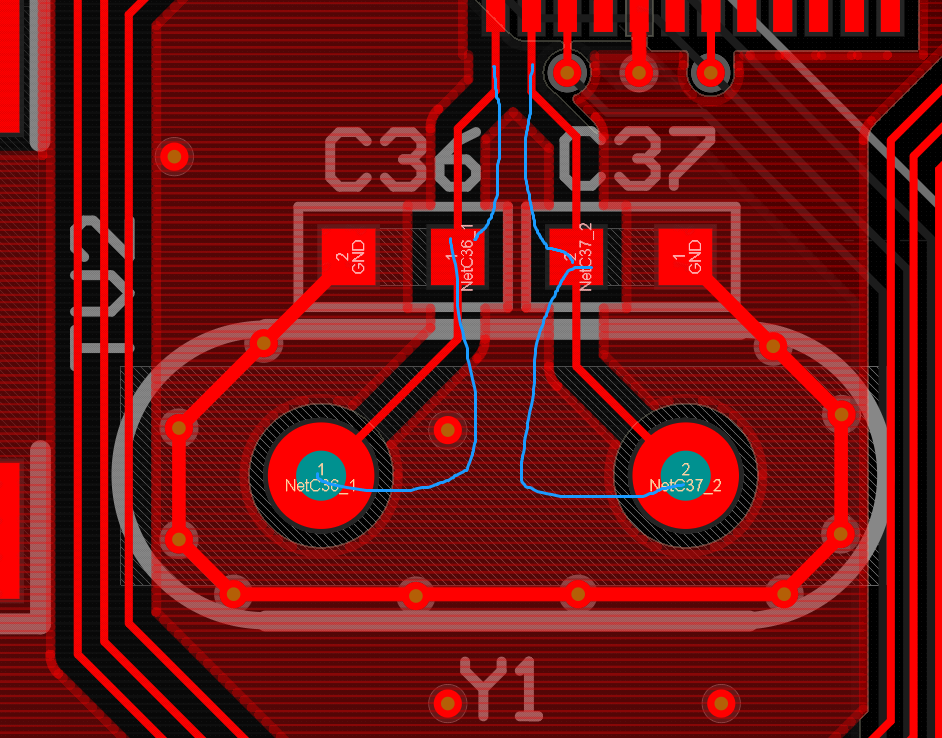

晶振走内差分需要再优化一下2.地分割间距最少1mm,建议2mm,有器件的地方可以不满足3.反馈信号走线需要加粗4.电感中间挖空就不要有铜皮5.输出打孔要打在电容后面6.注意过孔尽量盖油,不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特

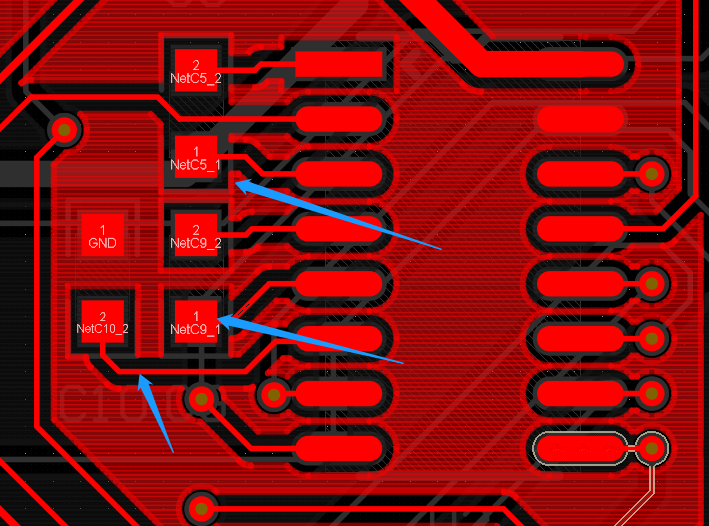

1.232的升压电容走线需要加粗2.走线尽量不要从小电阻电容中间穿线,容易造成短路3.USB走线不满足差分间距规则,可以打孔4.焊盘出线需要优化一下,拉出焊盘在进行加粗5.晶振需要包地处理,其他信号线不要从晶振里面穿6.USB差分对内等长5

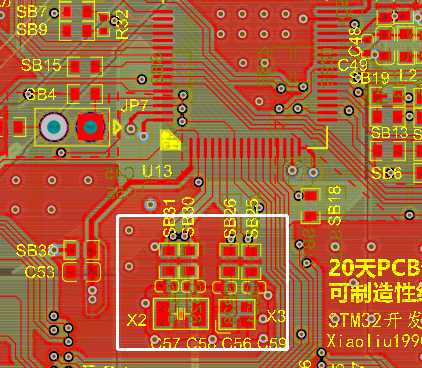

晶振可以在靠近管脚一些。差分锯齿等长不要大于两倍间距散热过孔正反都要开窗处理走线不满足3w间距这里输出要加粗处理电容按先大后小放置走线不要穿过电容电阻

器件摆放太近,建议2mm2.晶振尽量靠近芯片摆放,走内差分,并包地处理3.注意TX,RX等长线之间需要满足3W规则4.TX整组包地少一根TXD35.电源信号可以在电源层处理6.此处差分走线需要优化一下7.变压器除产信号外,其他的都需要加粗到

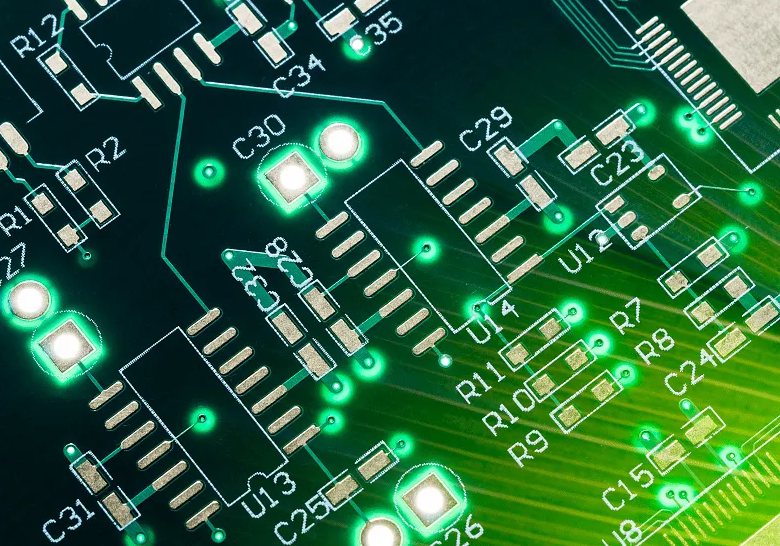

一个学习信号完整性仿真的layout工程师在PCB设计中,晶振(晶体振荡器)是非常重要的电子元器件,相信大部分的PCB工程师对它都不会陌生。因为晶振是属于重要的器件,对于layout和布局都是要重点关注的,比如走线要尽量短,周围要包地处理。

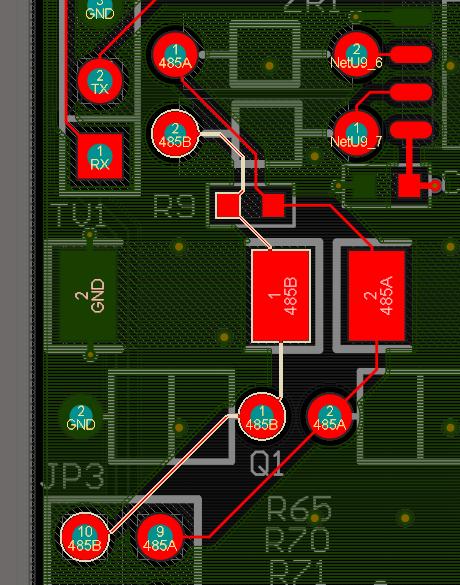

1.485走类差分需要优化一下2.模拟信号走线需要加粗处理3.晶振走线需要优化一下,尽量走类差分处理4.差分对内等长误差5mil5.跨接器件旁边要多打地过孔,分割间距建议1.5mm,有器件的地方可以不满足6.模拟信号呈一字型布局,走线加粗7

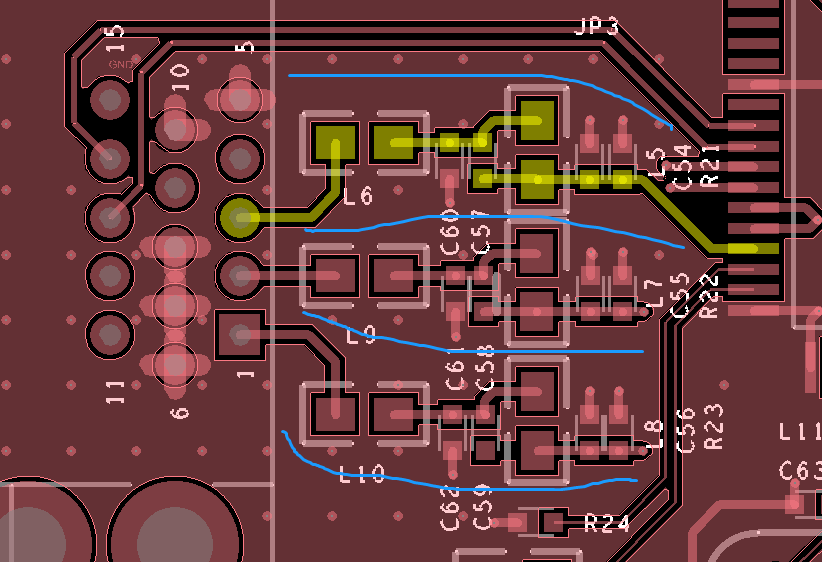

模拟信号需要一字型布局,单根包地处理2.晶振需要走内差分处理3.跨接器件旁边尽量多打地过孔,间距最少1mm,有器件不满足可以忽略,其他地方要尽量满足4.差分走线要尽量耦合5.百兆出差分信号外,其他信号都需要加粗到20mil6.模拟信号需要一

为什么你的晶振又烧坏了?

首先要清楚的一件事情是:晶振分为无源晶振与有源晶振两大类。基于这两类晶振的内部结构与工作原理的差异,晶振被烧坏的情况也要分为两大类:针对无源晶振被烧坏的情况有以下两点:1、手焊操作不当假如利用高温或长时间对导脚部位进行加热,会导致晶振内部晶

基于单片机的门控系统电路原理图如下: 制作出来的实物图如下: 元件清单: 单片机*1 11.0592晶振*1 瓷片电容22*2 电阻10k*1 电解电容10μF*2 四脚按键*3 DC电源座(3.5mm)*1、 LED红灯(3mm)*

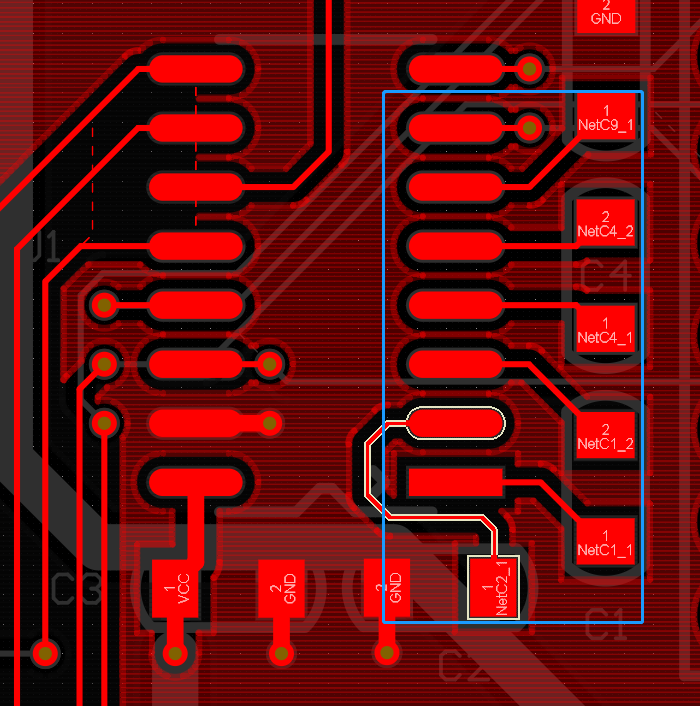

RS232的升压电容走线需要加粗处理2.USB差分对内等长误差5mil3.注意焊盘出线规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.注意电池供电,走线需要加粗处理,满足载流5.SD卡数据线误差尽量控制300mil6.晶振尽量包地

扫码关注

扫码关注