- 全部

- 默认排序

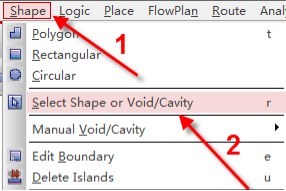

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

答:在前面的问答中,我们讲述了静态铜皮与动态铜皮的区别,为了更方便的进行设计,我们可以对两种属性的铜皮进行转换,具体的操作步骤如下所示:

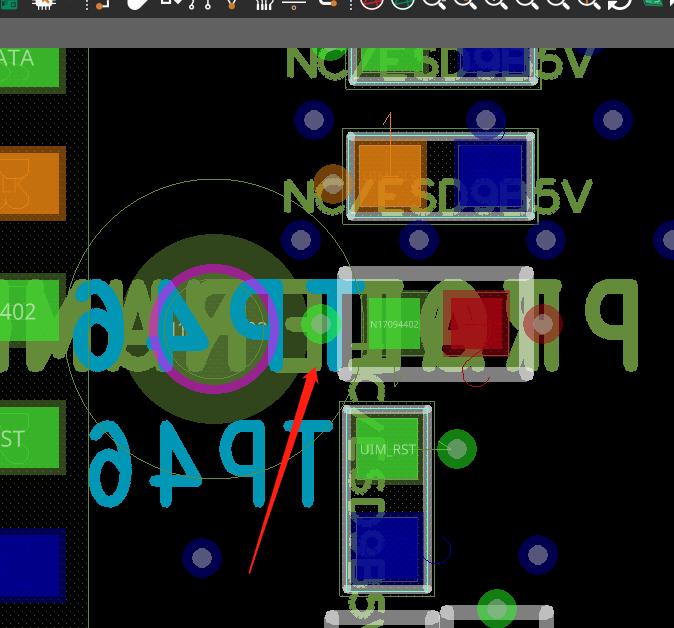

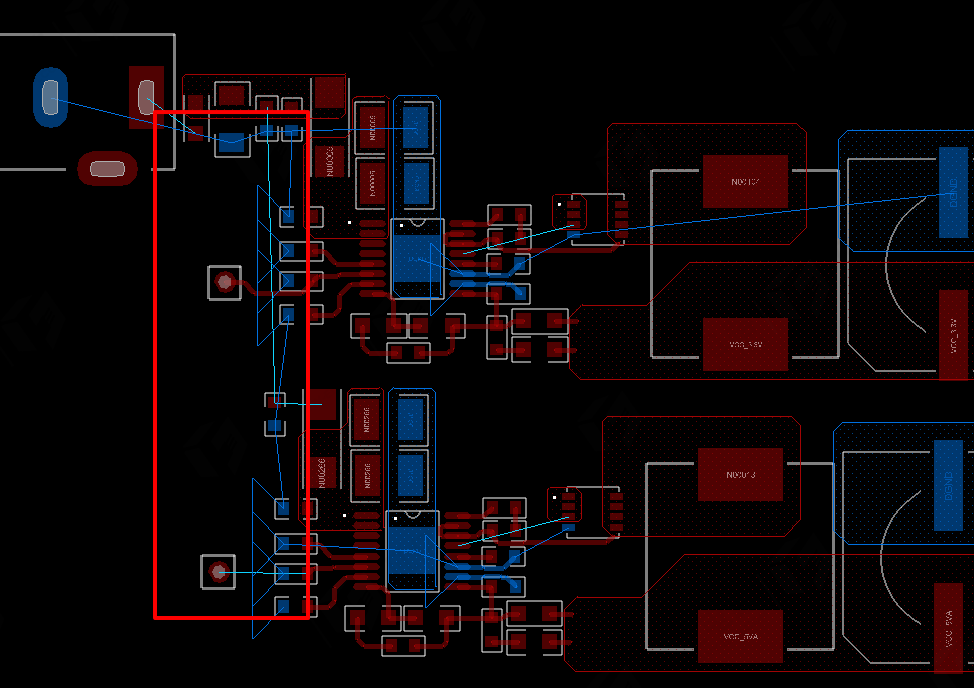

SIM:注意测试点跟器件以及过孔的间距,此处右侧器件可以整体往右边挪动一点:注意铜皮尽量设置动态铜皮,将静态转换下:电感内部挖空掉,在当前层:TF:注意器件之间可以空出点间距留出来扇孔,扇孔不要离焊盘太远:时钟信号包地保全一点,还有 空间可

PADS覆铜平面

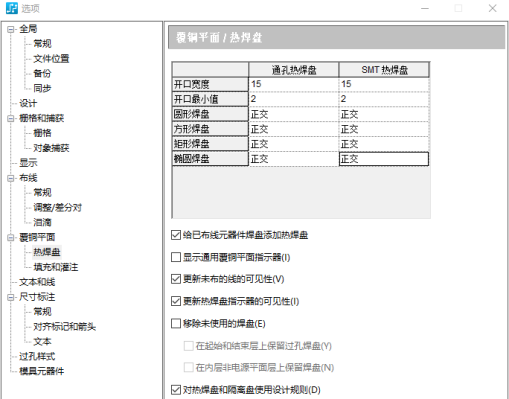

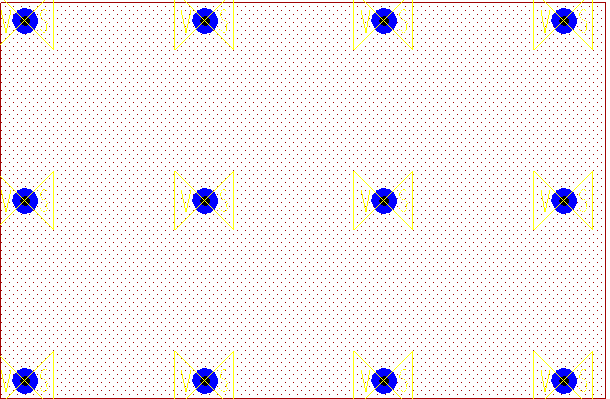

覆铜平面是动态铜皮类型,即绘制好铜皮后,碰到障碍物,覆铜后期形状会规避障碍物,以免DRC生成。1)覆铜平面添加步骤与铜箔操作基本类似,首先执行菜单命令中“工具-选项”或者使用组合快捷键“Enter+Ctrl”,设置“热焊盘”选项,如图5-1

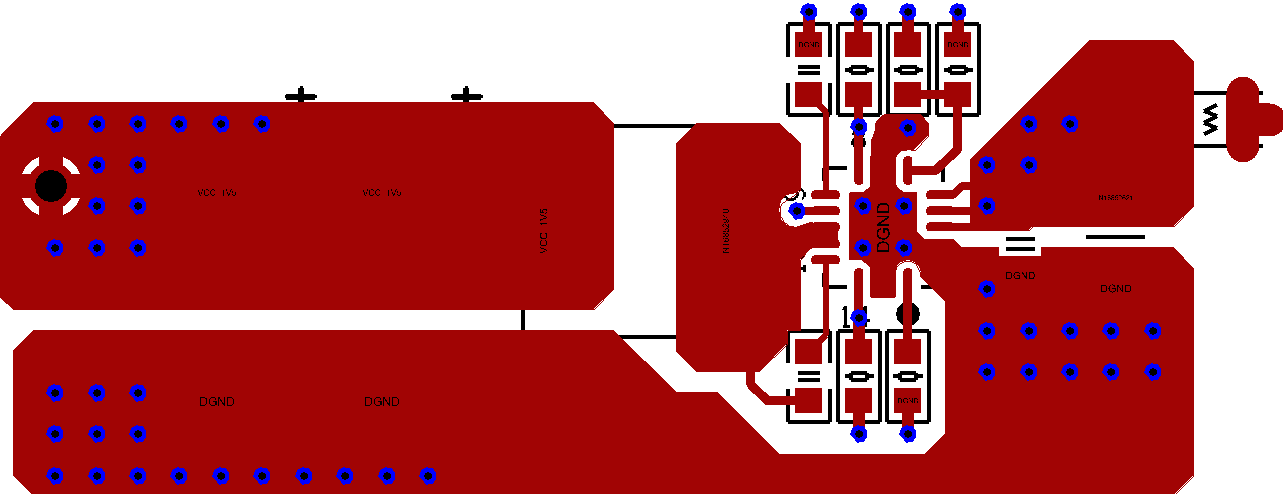

答:我们在Allegro软件中,铺铜的时候,有两种铜皮可以选择,一种是静态铜皮,一种是动态铜皮,如图6-101所示,是静态铜皮,如图6-102所示,是动态铜皮。

请教一下,allegro的pcb,导出gerber的时候,需要把板子上的动态铜皮全都转成静态铜皮吗?

多处飞线没有连接铺铜尽量用动态铜皮电源输出路径铺铜加宽载流,按原理图顺序放置封装反馈路径应连接到电路最后端,走线即可主输出和反馈信号正确示范一路dcdc电路地信号连接通,在芯片下方打孔接地相邻电路电感应朝不同方向垂直放置问题很多,需要认真改

扫码关注

扫码关注