- 全部

- 默认排序

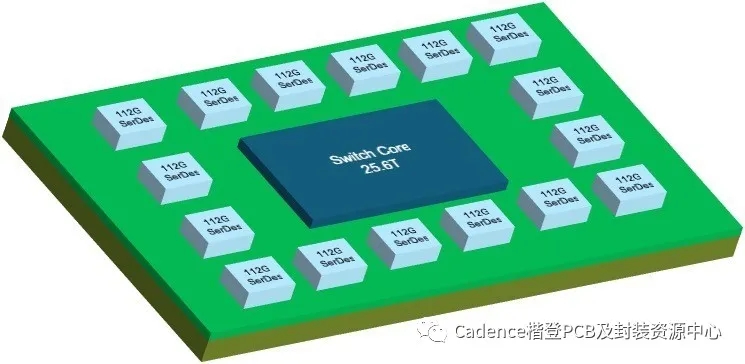

HOT CHIPS大会上的演讲将设计分割成处理器本身和设计的I/O部分。处理器可以采用最先进、最昂贵的节点制造,而I/O则可以采用不够先进、较便宜的节点制造(通常落后一代)。下方图片是Intel的Lakefield芯片,它有一个I/O基片(采用非前沿的14纳米制程),10纳米制程的处理器,以及封装在顶部的动态随机存取存储器(DRAM)。这些都采用Intel的Foveros 3D技术组装。

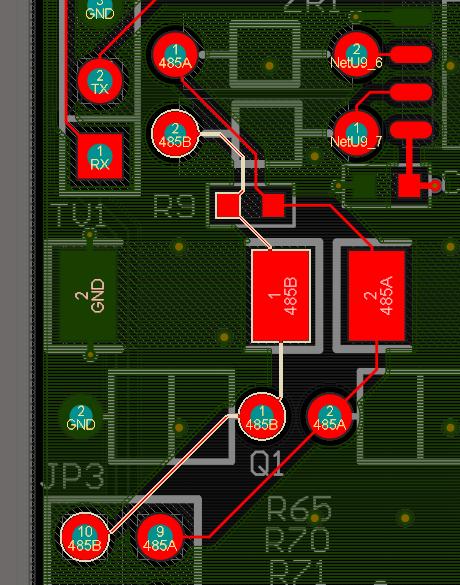

1.485走类差分需要优化一下2.模拟信号走线需要加粗处理3.晶振走线需要优化一下,尽量走类差分处理4.差分对内等长误差5mil5.跨接器件旁边要多打地过孔,分割间距建议1.5mm,有器件的地方可以不满足6.模拟信号呈一字型布局,走线加粗7

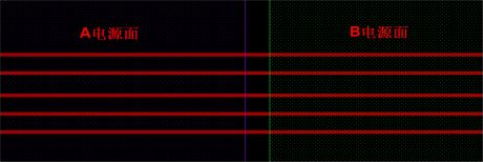

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割现象示意图跨分割,对于低速信号可能没有什么关系,但是在高速

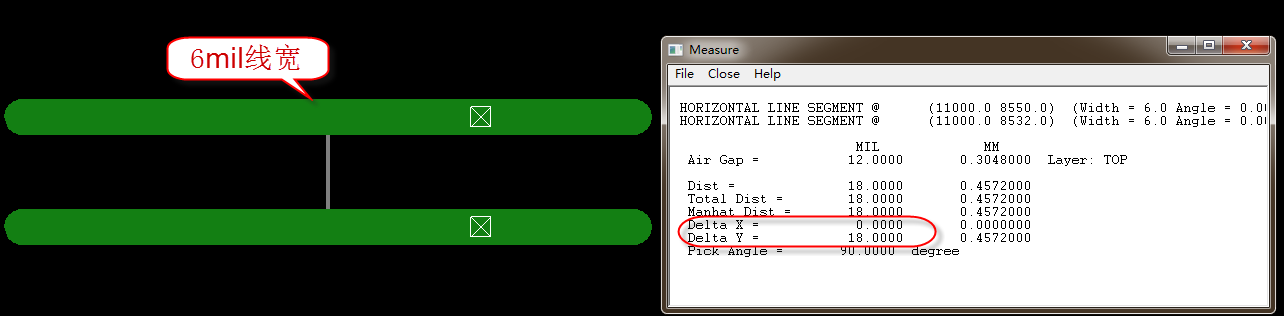

答:第一,3W原则,在PCB设计中很容易体现,保证走线与走线的中心间距为3倍的线宽即可,如走线的线宽为6mil,那么为了满足3W原则,在Allegro设置线到线的规则为12mil即可,软件中的间距是计算边到边的间距,如图1-38所示. 图1-38 PCB中3W原则示意图第二,20H原则,在PCB设计的时候,为了体现20H原则,我们一般在平面层分割的时候,将电源层比地层内缩1mm就可以了。然后在1mm的内缩带打上屏蔽地过孔,150mil一个,如图1-39所示。 图1

高速PCB板的设计方法

直播结束后扫码添加助教领取课件背景介绍:高速PCB板的信号频率以及传输速度比一般的板子高很多,有些信号速率甚至能达到20G以上,所以我们在设计的时候需要考虑信号的完整性,抗干扰能力等等,需要结合结构工程师和硬件工程师多方面考虑布局布线。高速

扫码关注

扫码关注