- 全部

- 默认排序

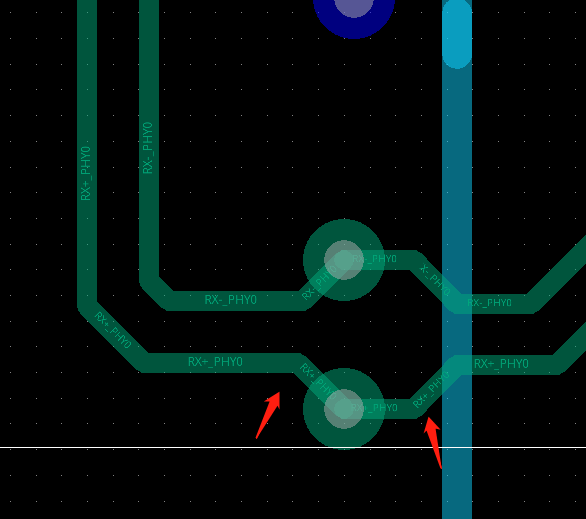

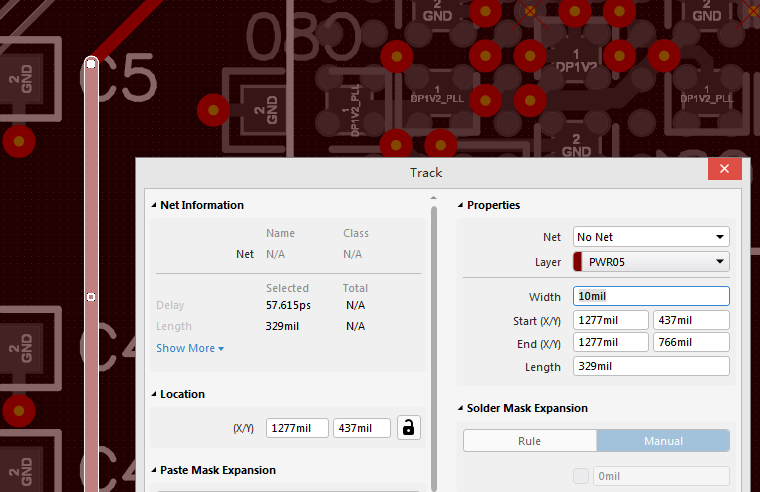

注意差分走线,此处的右边调整为左边形式走线:注意地网络顶层也没铺铜,GND层也没有进行负片分割,需要重新设计:PWR层也没有设置负片层进行分割或者是正片铺铜,建议重新设计下:电源跟地都没有处理。TX RX没有设置MGROUP等长:差分需要对

Cadence Allegro16.6 两层stm32最小系统主板pcb视频教程,PCB设计全功能模块,进阶实战案例。STM32F103C8T6最小系统方案,原理图库+SCH+PCB库+Layout设计,双面板电源+地分割解析。

敷铜在PCB设计当中不可能一步到位,但是根据敷铜的最后结果,我们还是可以再次进行编辑的,此小视频是为了方便大家如何学习好这个操作

地分割间距最少保持1.5mm2.中间的热焊盘上尽量不要走线,后期自己更换一下走线路劲3.电源线宽尽量一致,满足载流4.走线没有连接到过孔中心,存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链

业界普遍认为,混合波束赋形将是工作在微波和毫米波频率的5G系统的首选架构。这种架构综合运用数字 (MIMO) 和模拟波束赋形来克服高路径损耗并提高频谱效率。如图1所示,m个数据流的组合分割到n条RF路径上以形成自由空间中的波束,故天线元件总

答:一般处理模拟地、数字地的方法有以下几种:直接分开,在原理图中将数字区域的地连接为DGND,模拟区域的地连接为AGND,然后PCB中的地平面分割为数字地与模拟地,并吧间距拉大;数字地与模拟地之间用磁珠连接;数字地与模拟地之间用电容连接,运用电容隔直通交的原理;数字地与模拟地之间用电感连接,感值从uH到几十uH不等;数字地与模拟地之间用零欧姆电阻连接。总结来说,电容隔直通交,造成浮地。电容不通直流,会导致压差和静电积累,摸机壳会麻手。如果把电容和磁珠并联,就是画蛇添足,因为磁珠通直,电容将失效。

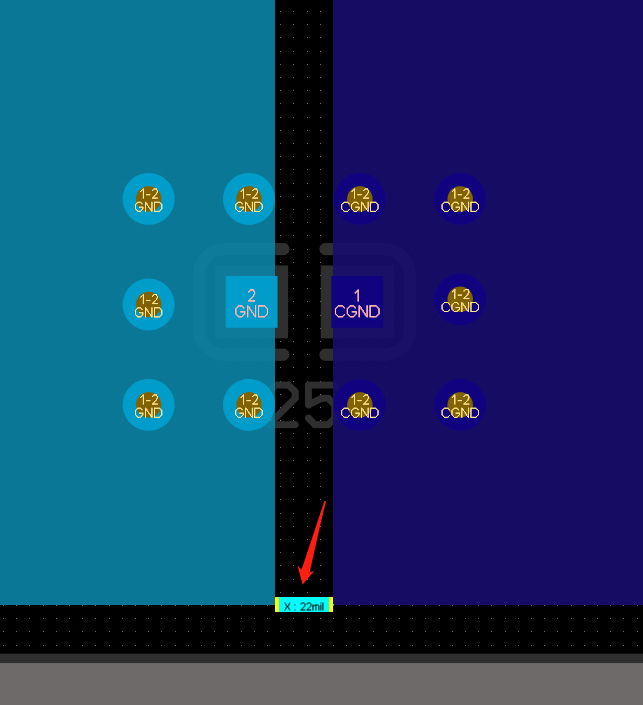

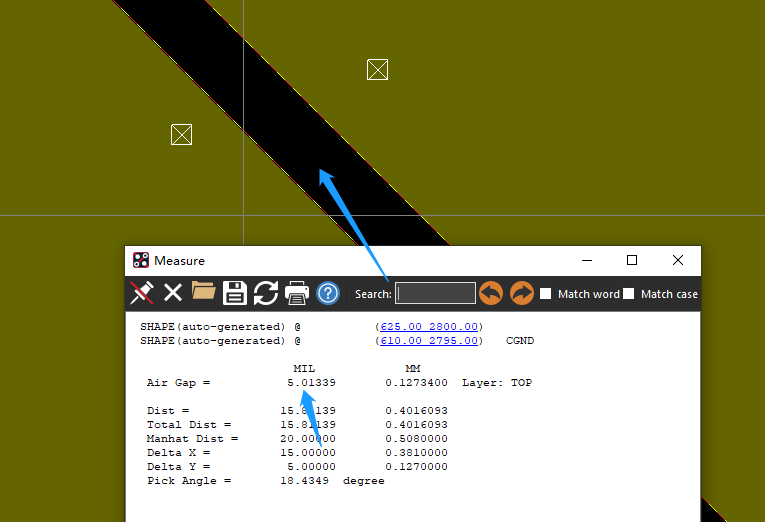

建议平面层的分割带宽度至少20MIL:地址信号类的等长还存在个别信号的误差报错:误差报错的信号自己再去等长优化。建议地址跟数据线两个类之间的信号可以走一根GND信号线进行分割开:或者自己预留20MIL的宽度。整个电源平面的信号都是3.3V信

地分割间距要保证2mm,有器件的地方可以不满足2.网口除差分信号外,其他的都需要加粗到20mil3.晶振需要包地处理,并在地线上4.BGA里面的铜皮建议挖空处理5.焊盘到孔的间距过近,建议6mil,后期自己优化一下以上评审报告来源于凡亿教育

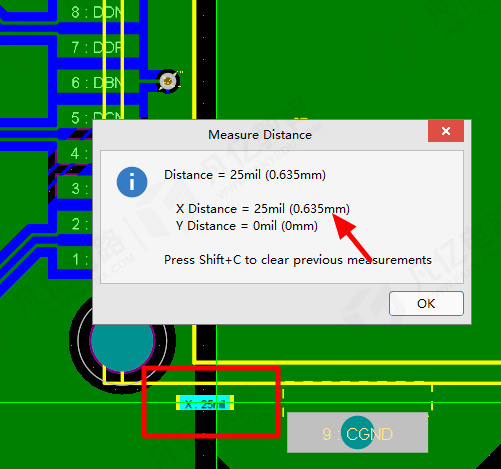

cgnd到gnd分割距离要2mm以上cgnd到gnd跨接处,两端多打过孔底层gnd铜皮被走线分割,导致多处孤岛铜皮,两层板尽量走线在一层,留一个尽量短的回流路径过孔不要上小器件焊盘多处尖岬铜皮等长绕线不要绕出直角以上评审报告来源于凡亿教育9

扫码关注

扫码关注