- 全部

- 默认排序

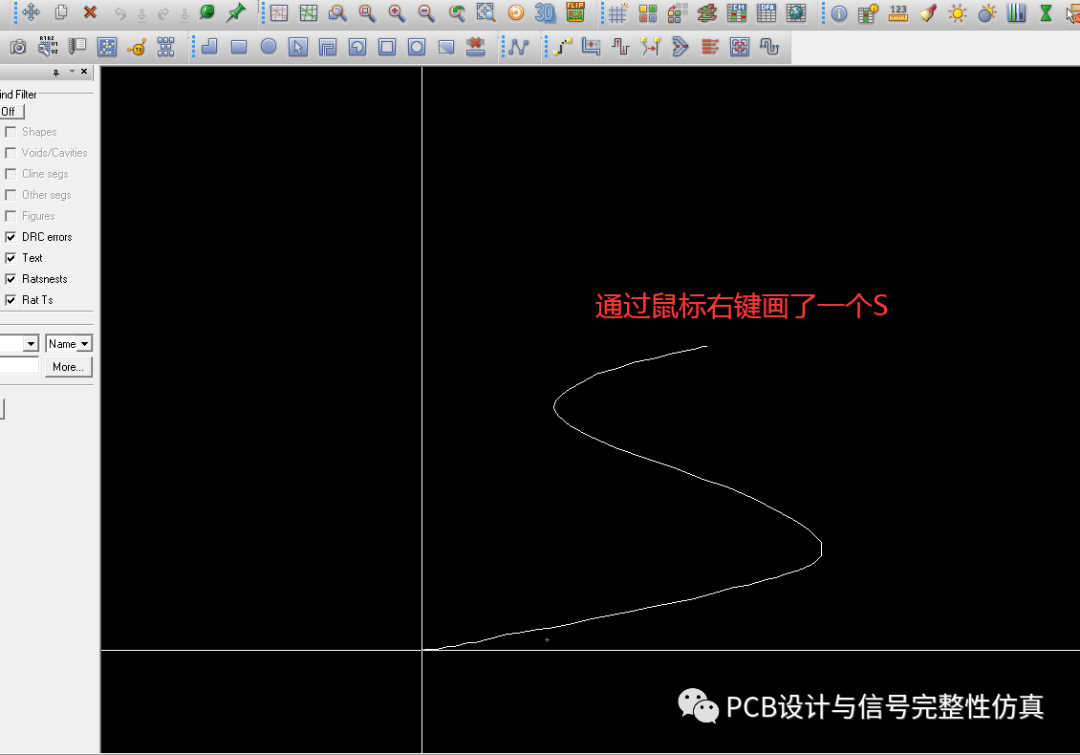

利用键盘快捷键,已经可以大幅提高设计速度。但对于使用习惯来说,通常是左手键盘,右手鼠标。因此快捷键搭配鼠标,还是需要双手进行操作。

扫码添加助教领取更多学习资料此课程套餐包含四套课程(ALLEGRO/PADS/Altium三个版本,详情请看目录大纲,按照需求进行学习即可)1、EDA软件的基本操作(字幕版)2、2层PCB设计实战课程(字幕版)3、PCB设计工程师真人面试0

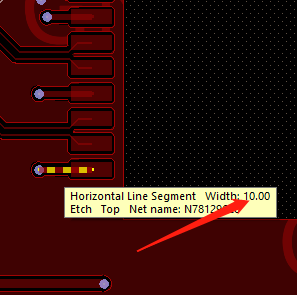

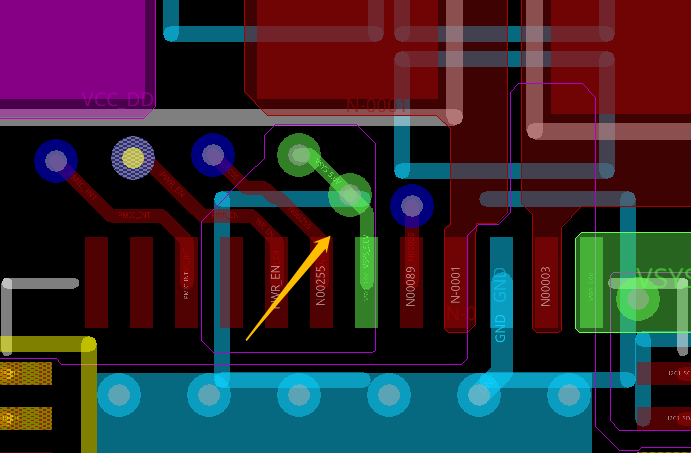

网口除差分信号外其他的都需要加粗到20mi2.跨接器件两端需要多打地过孔3.晶振信号需要包地处理,下面尽量不要放置器件存在DRC报错注意等长线之间需要满足3W规则电源注意线宽尽量保持一致,满足载流以上评审报告来源于凡亿教育90天高速PCB特

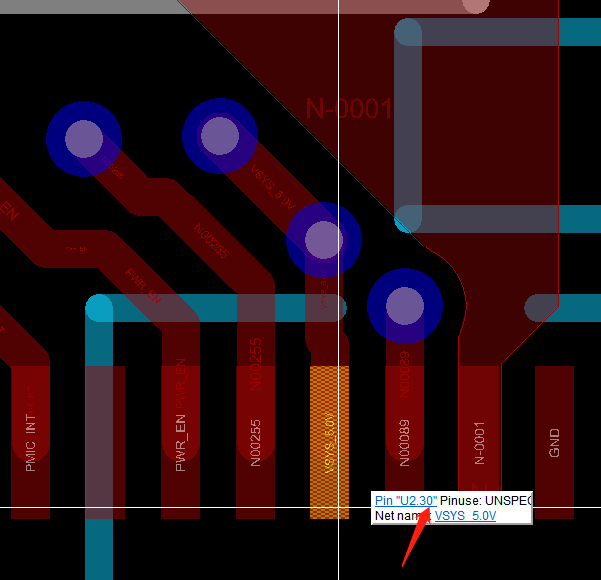

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

此处不满足载流2.此处存在开路3.输出打孔要打在滤波电容后面5.反馈线要从滤波电容后面取样,走10mil即可6.电感所在层的内部需要挖空处理,背面尽量不要放置器件7.电源网络需要再底层铺铜进行处理,剩下的地方铺地以上评审报告来源于凡亿教育9

扫码关注

扫码关注