- 全部

- 默认排序

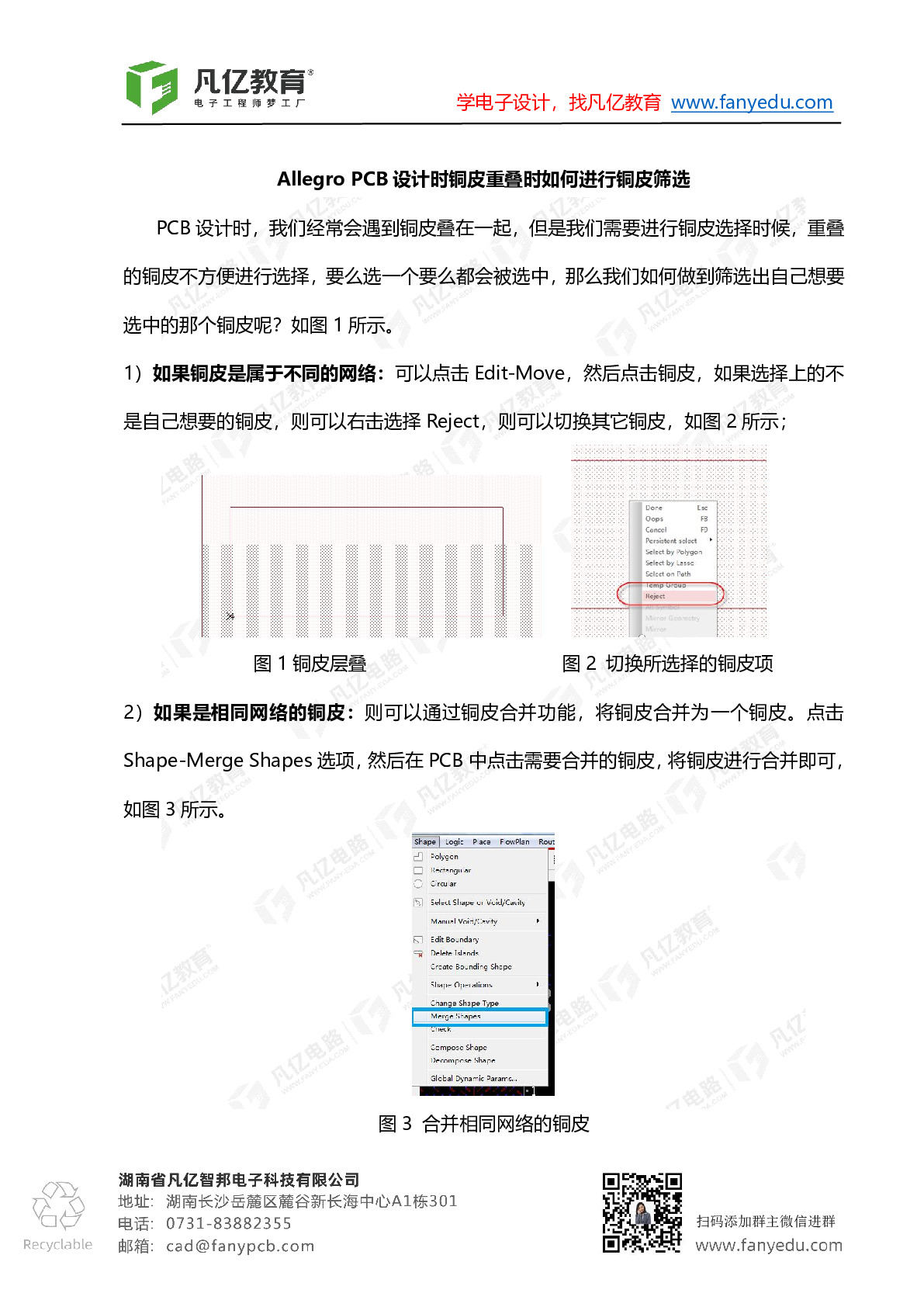

(SPMHAC-33): Cannot Add Via. Working Layers are not defined.(SPMHAC-33): Cannot Add Via. Working Layers are not defined. 本来好着,突然不能打孔了,又遇到这样的吗,

net group、 match group、net class它们之间的区别还有作用是什么?

在PCB设计完成后,很多电子工程师不仅要将Gerber文件给制造厂商,也要提供坐标文件,保证PCB制造顺利,那么ALLEGRO如何生成坐标文件?其中有哪些文件?下面一起来看看吧!1、要提供那些文件?①Gerber文件中的Pastemask层

最近电子工程师的就业市场显然有些低迷,越来越多大厂宣布开始裁员,甚至缩减了招聘岗位降低薪资,那个被无数问到的问题再次被提及“电子工程师的未来是不是会大量失业?”首先表明下我的观点:会,但原因并不是来自最近火爆的“AIGC”,而是这个行业发展

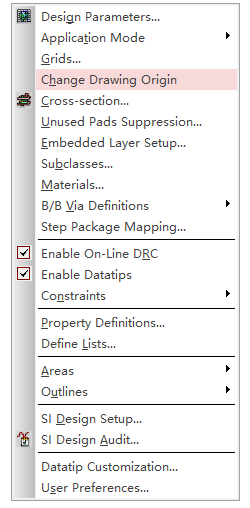

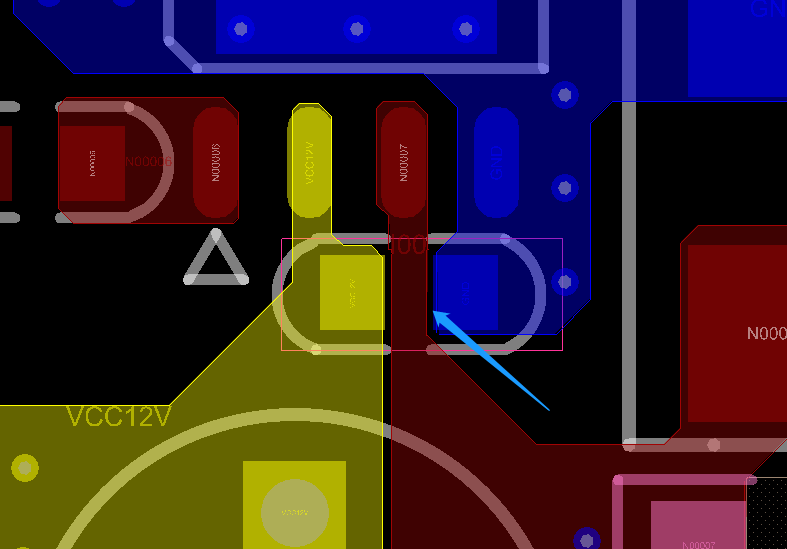

注意差分走线,此处的右边调整为左边形式走线:注意地网络顶层也没铺铜,GND层也没有进行负片分割,需要重新设计:PWR层也没有设置负片层进行分割或者是正片铺铜,建议重新设计下:电源跟地都没有处理。TX RX没有设置MGROUP等长:差分需要对

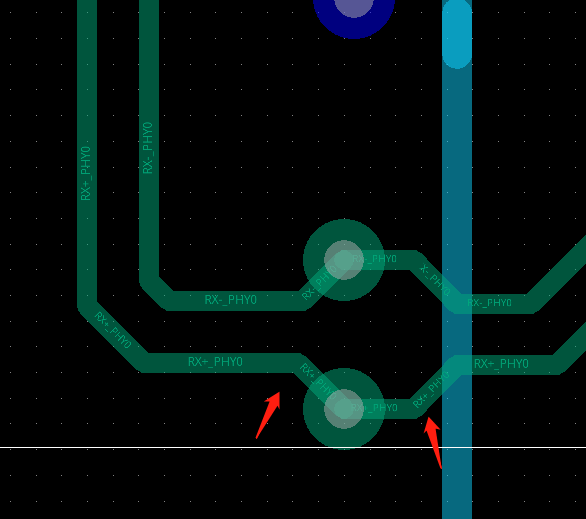

座子需要靠近板框放置2.电源输出主干道尽量铺铜处理,满足载流3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.电容保持先大后小原则5.反馈路劲从电容后面取样,走线远离电感6.此芯片采用单点接地,就是输入输出的地要接到芯

确认一下此处是否满足载流,铜皮尽量不要铺到电容中心,容易造成短路每路都存在一样的问题,后期自己调整一下器件摆放的位置,把铜皮加宽2.器件摆放尽量中心对齐处理3.器件摆放注意方向尽量一致,对齐处理;4.pcb上还存在开路5.座子需要靠近板框外

扫码关注

扫码关注