- 全部

- 默认排序

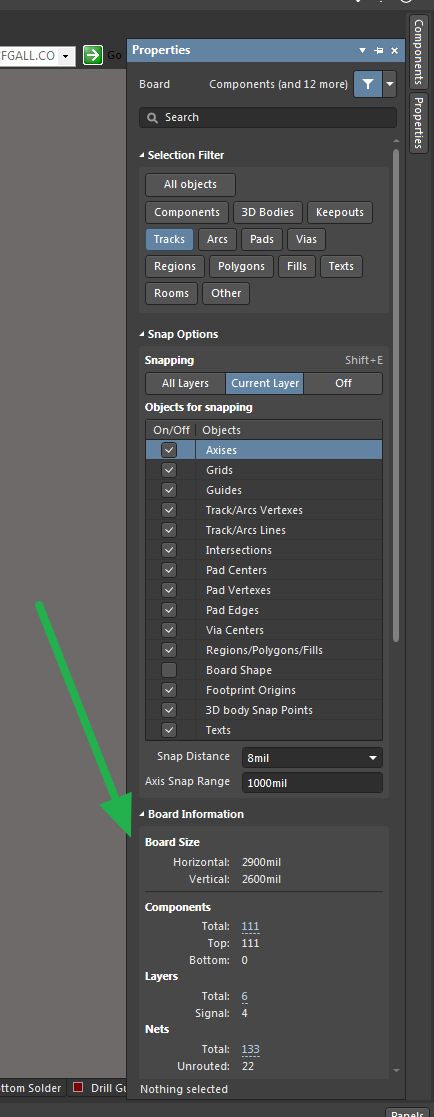

Ad19由于做了更新的改动,所以我们对应的RB就不能进行管脚的查看,首先我们点击我的PCB界面,然后我们点击我们的PCB的空白处,我们点击一下,然后我们对应在我们的panel 面板下面调用出我们的proprieties这个界面,这个和低版本不一样之处在于,高版本将prorieties这个界面替代了我们的PCB Inspertor.

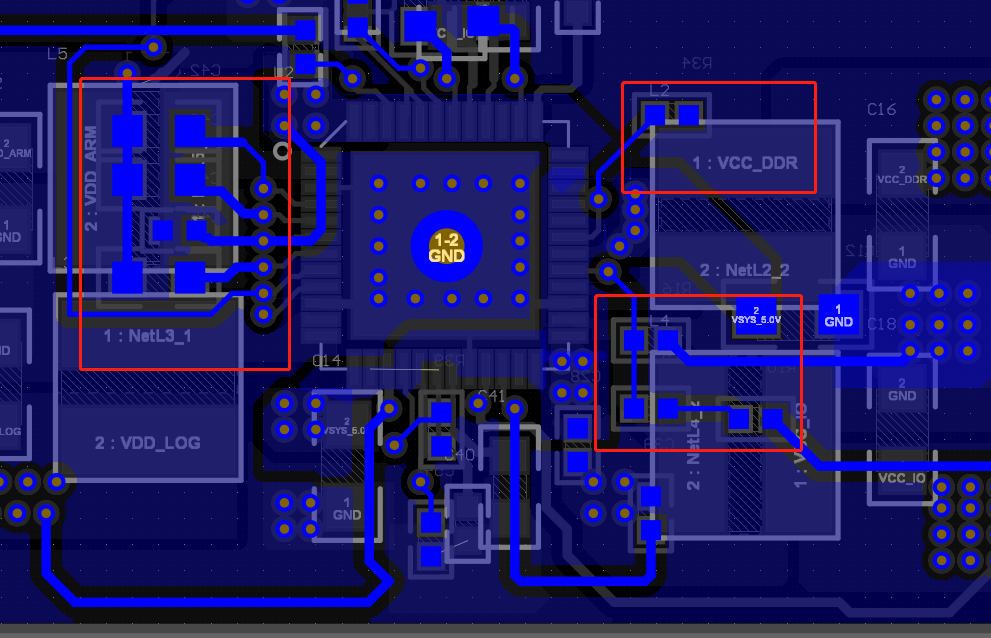

电感底部不能放置器件,以及走线,自己优化吧电感下面的器件塞到芯片底部:布局需要改动。器件并未对齐,并且都干涉了:器件是需要整体的中心对齐放置。上述一致原因的布局问题:布局需要优化,中心对齐好,器件之间不要干涉。DCDC电源主干道的电容是要靠

座子需要靠近板框放置2.不要随意改动原理图所需要用的封装3.此处走一根10mil的线即可,不用进行铺铜4.电感所在层的内部需要挖空5.输出电容按照先大后小顺序摆放,不要修改电容封装后期自己按照原理图自己调整封装6.器件摆放注意中心对齐处理,

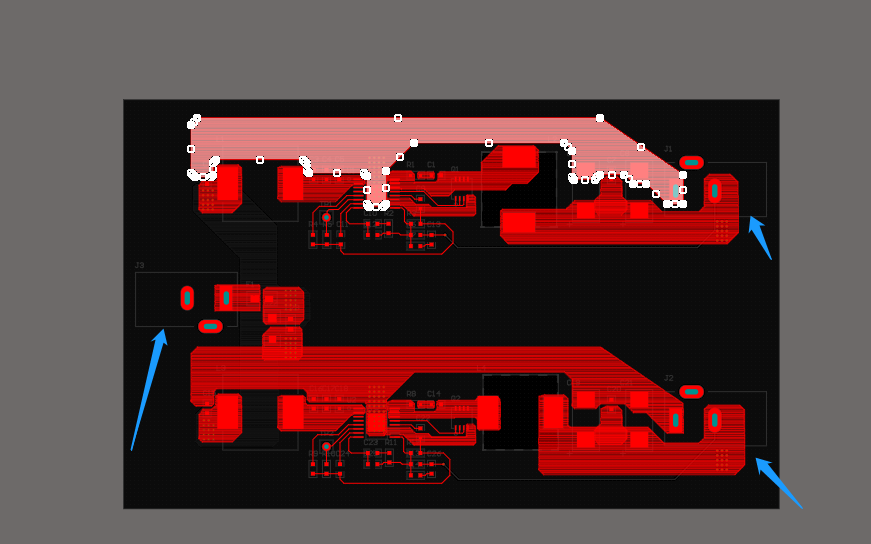

allegro 在画完pcb及已经动态敷铜了,但后面又需要改动线路时,铜皮不避让布线。这是什么情况?

我的乘法已经写了好久了,但是一直改来改去,今天终于完成了算是比较标准的一个程序吧,我把所有端口的宽度都用一个变量来表示,到时候直接改动变量的值就可以了。。。 之前,我给变量赋值的语句是这么写的: parameter e1=4'd8;///表示成数的指数位数//// parameter e2=4'd8

大家有没有听过软件设计中的低耦合,高内聚的两个原则。具体是什么意思呢?在一个项目中:每个模块之间相联系越紧密,则耦合性越高;这样你改动其中一个模块,其他模块也需要一起改动,换言之:牵一发而动全身。一个模块内部各个元素之间的联系的紧密程度,如

实现硅稳压管稳压电路需要什么条件-硅稳压管稳压电路如图1所示。当稳压管作业在反向击穿状况时,假定输入直流电压有不坚决或负载发作改动,将会使UO有改动的趋势,这时Iz会发作剧烈改动,经过限流电阻R两头电压的改动来抵偿输入电压或负载的改动,然后抵达了安稳UO的意图。

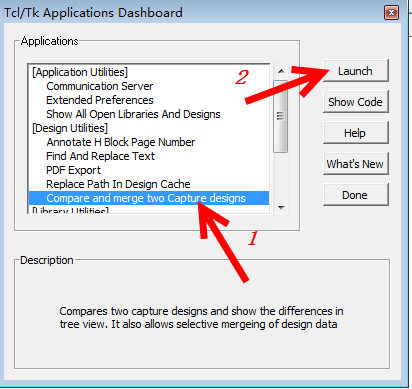

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注