- 全部

- 默认排序

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

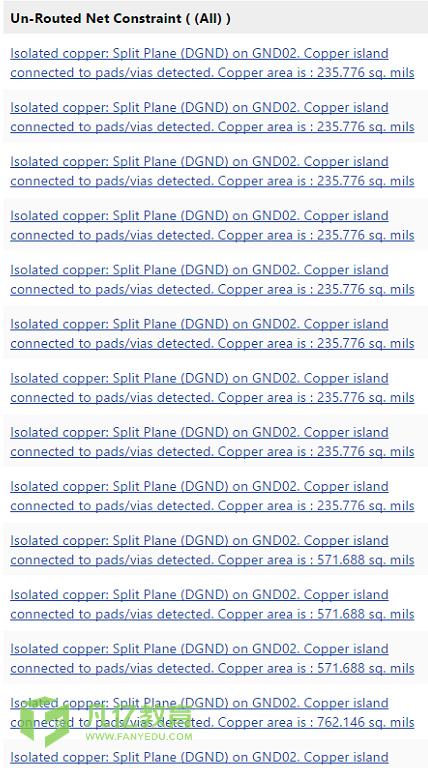

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

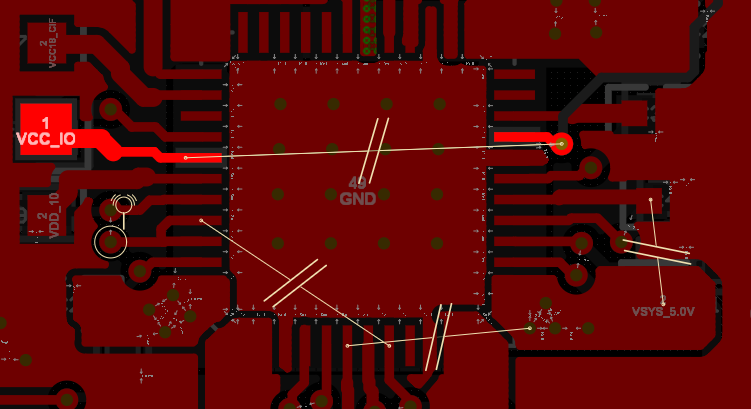

还存在多处开路报错:看下此处是什么元素跟元素的间距报错:检查了对应自己修改。电感底部不要放置器件 ,净空,自己重新布局下:并且电感内部挖空处理:看下此处VCCIO线宽是否满足其载流大小:处理下多余线头删除,连接到过孔中心:走线不要出现直角:

我画的封装,所有引脚的间距和宽度都是一样的,怎么导入到PCB中,有一些引脚报错,请问 请问在哪里设置呀

全站最新内容推荐

- 1PCB设计有必要去掉死铜吗?

- 2CCM和DCM到底是什么?有什么区别?

- 3多门元件导入layout后有多个封装,每个门对应PCB封装的特点管脚,这是为什么

- 4双通道 2x2 Wi-Fi 6 四核ARM 通信处理器:BCM47622A0IFEBG、BCM47622A1KFEBG

- 5PDAS 元件的每个门在导入layout的时候都有一个PCB封装,最后layout里有多个封装,这是为什么呢?

- 6(器件)88W9064-A1-BWPC/AK 双频Wi-Fi® 6 (802.11ax)接入解决方案,8A34001E-000AJG8时钟同步器 IEEE 1588 八通道

- 7中英文界面切换

- 8(电源管理ic)INN3670C-H615-TL、INN3670C-H606-TL 离线转换器 反激,次级侧 SR 拓扑 60kHz InSOP-24D

- 9走进电子元件,了解声控传感器

- 10PCB温升现象产生原因及热效应详解

扫码关注

扫码关注