- 全部

- 默认排序

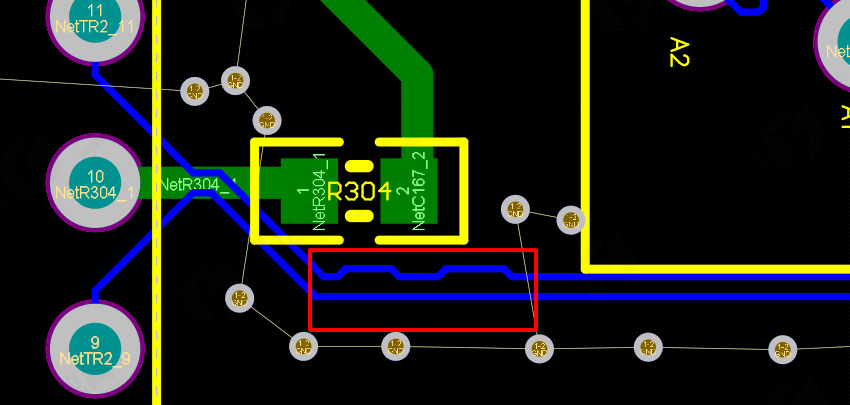

差分对内等长错误,按照等长绕线高度和长度不符合规范焊盘没有开窗相邻器件尽量朝相同方向整齐放置走线避免锐角对内等长误差不达要求,差分对内等长误差要求在5mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

PCB Layout是一款功能强大的PCB设计软件,相比其他EDA软件,Pads Layout偏重于PCB布局,因此被广泛应用在各种电子产品的开发中,在使用Pads Layout时,有些技巧可帮助提高提高设计效率和减少错误,下面来看看有哪些

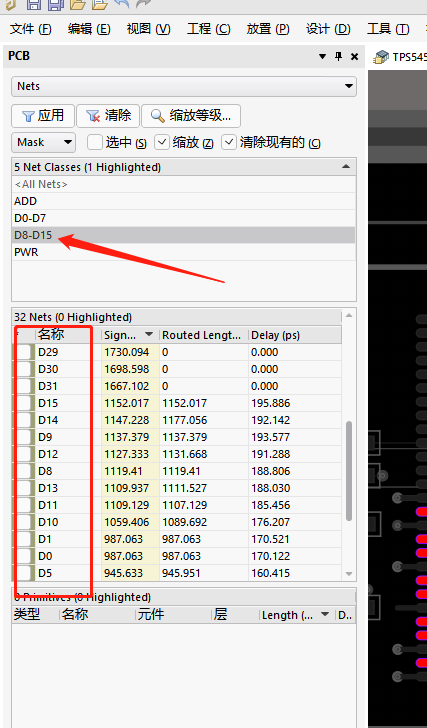

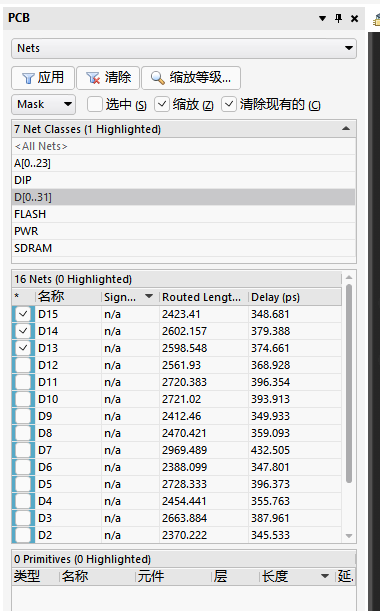

数据线一组只有9根线,其他信号不要添加进来,高八位少一根LDQM12.数据线和地址线建议添加一根最少20mil的地线进行隔开3.过孔里存在多余的线头4.地址线分组错误,有电阻几根网络也需要添加进来进行一起等长,还有时钟信号5.走线需要从焊盘

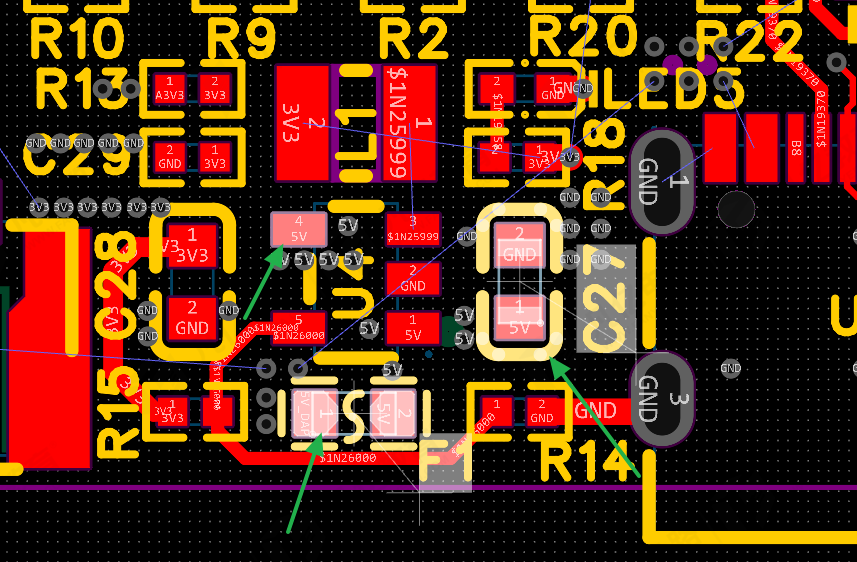

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

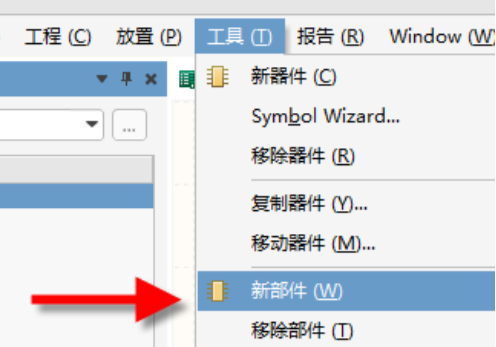

Altium Designer多部件原理图库/元件库的创建当一个元件封装包含多个相对独立的功能部分(部件)时,可以使用子件。原则上,任何一个元件都可以被任意地划分为多个部件(子件),这在电气意义上没有错误,在原理图的设计上增强了可读性和绘制

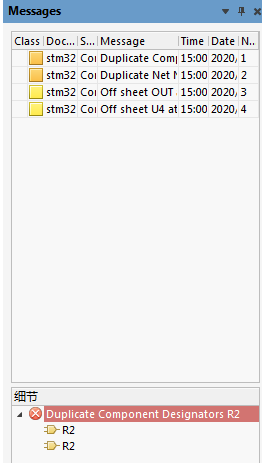

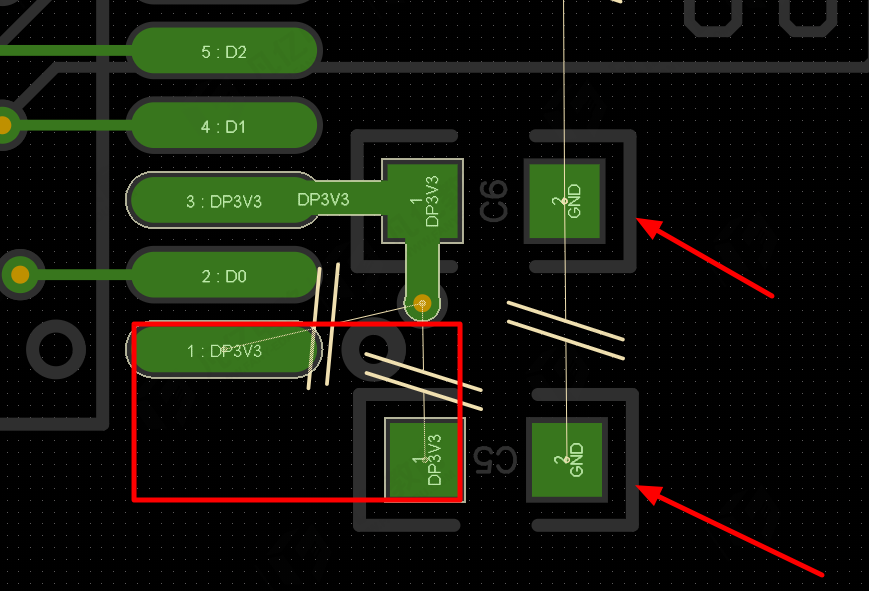

我们在编译完原理图之后有时会看见红色的波浪线,这些红色的波浪线时我们在编译后的错误显示,提示这个地方有错误。这时候我们只需要在“Messages”里面查看对应的错误类型并修改即可。

对电子工程师来说,Saber并不陌生,它是一款广泛以用于电力电子和电机驱动系统仿真的软件,但在实际使用过程中,工程师可能遇见一些常见的错误,本文将介绍Saber软件的常见错误及解决方法,希望对小伙伴们有所帮助。1、仿真模型错误①模型参数定义

1.电源存在开路,地焊盘很多没有打孔造成开路报错。2.1v2电源过孔没有连通,造成天线报错。3.电源扇孔走线没有加粗4.时钟线电容应该考近芯片摆放5.时钟线等长错误,应与地址线放一组一起等长。6.地址线分组错误,缺少部分信号7.地址线等长错

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

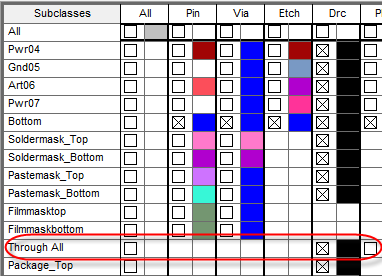

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

全站最新内容推荐

- 1LED驱动模块RSC6218A 5W-18W迷你高效驱动电源应用-REASUNOS(瑞森半导体)

- 2从零开始成为电子大佬,第一步先识读电源!

- 3IEEE 1588 四通道/八通道系统同步器:8A34001E-000AJG、8A34002E-000NLG、8A34003E-000NBG(器件)

- 4光电器件故障了,如何排除维护?

- 5走进电子元器件,了解热继电器

- 6搞电子设计的人,转行能干什么?

- 7Solder Mask和Paste Mask有哪些不同?

- 8PCB板制造技术水平的标志如何看?

- 9雷军招人:为中国汽车工业全面崛起做贡献!

- 10单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

扫码关注

扫码关注