- 全部

- 默认排序

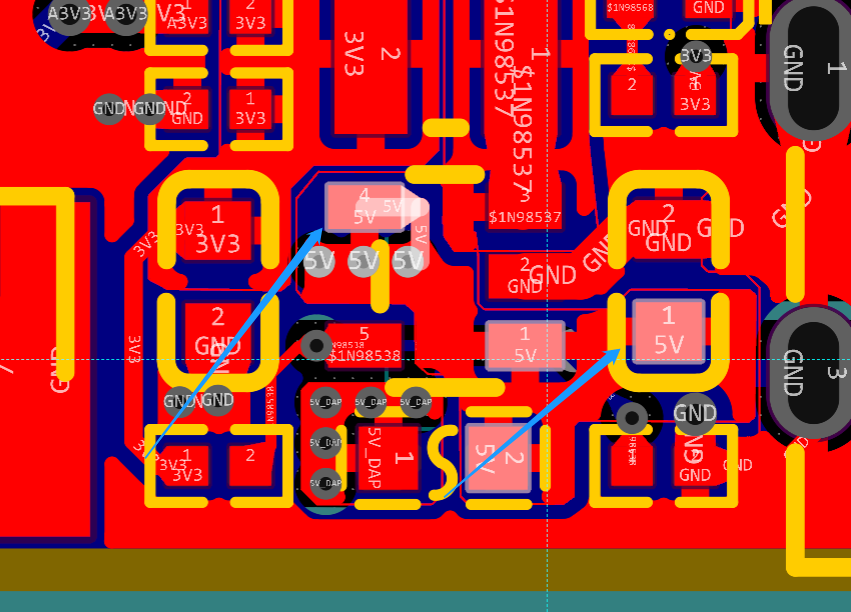

地缘信号走线需要加粗处理,尽量满足载流2.SD卡需要靠近板框放置3.SD卡信号线需要进行等长处理,误差300mil4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振需要走内差分,并包地处理,在地线上均匀的打上地过孔

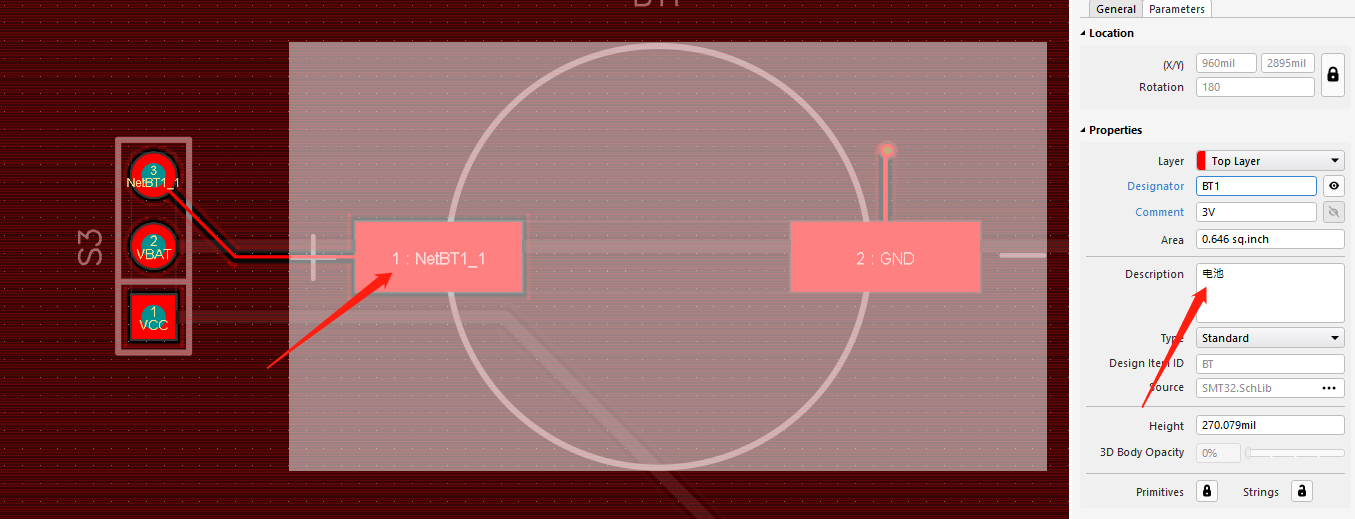

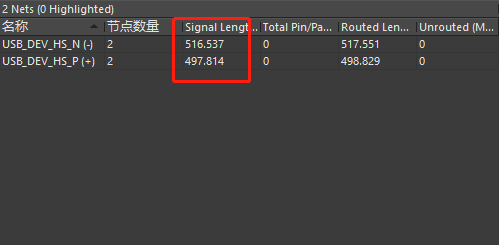

RS232这几个电容属于生压电容,走线需要加粗2.VBAT电源尽量加粗到20mil3.USB差分对内误差5mil4.差分包地,地线上尽量多打过孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

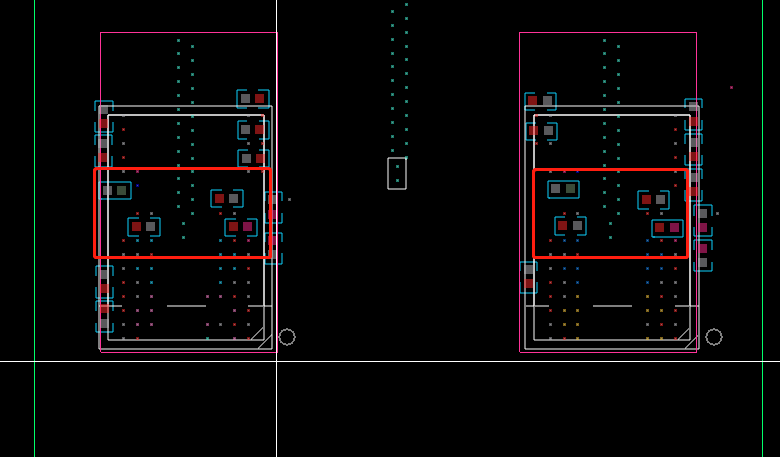

个别器件注意整体对齐:注意等长线之间需要满足3W间距原则:没满足的都自己优化下。数据线组内也需要满足3W:差分对内等长误差为5MIL:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

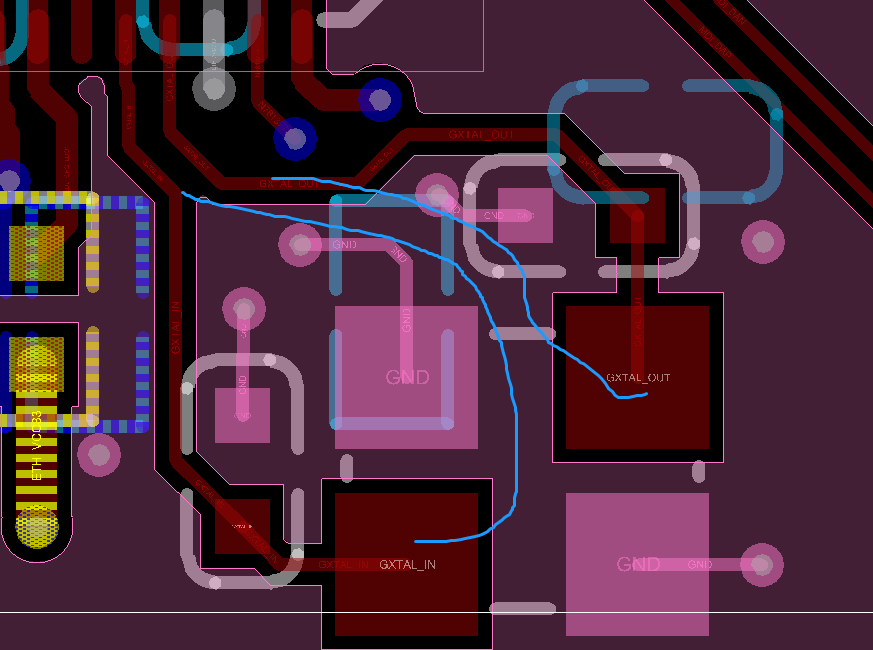

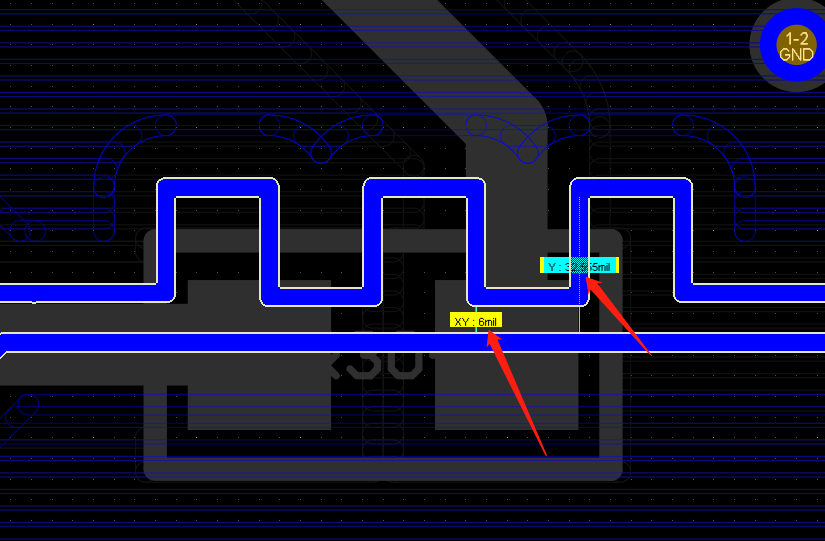

晶振需要走内差分,并且包地打地过孔2.变压器所有层需要挖空处理3.差分线处理不当,锯齿状凸起高度不能超过线距的两倍4.此处差分走线不满足差分间距规则5.差分对之间不用进行等长,差分对内等长即可,误差5mil6.此处需要添加一个2MM的隔离带

在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Allegro PCB设计者来说,我们在等长的时候经常会提到X-NET,利用X-NET功能我们能够很快的计算多点拓扑结构等长长度,并且还能够计算数据组等长误差,很是方便,但是我发现在给很多学员教学的过程中,很多人不清楚这个功能的使用,那么我们这次抽时间弄成一个专题来详细的给大家讲解一下。

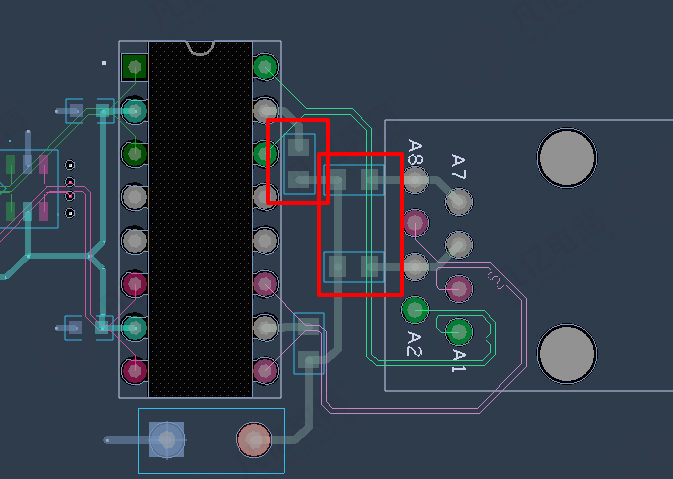

1.器件摆放重叠,应保持一定间距2.差分对内等长错误3.时钟线需要包地打孔处理4.多处飞线没有连接5.以太网芯片到CPU的GMII接口线的发送部分需要等长,建立rx、tx分别等长控制100mil误差范围6.差分没有建立对内等长规则,差分对内

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

差分线锯齿状等长不能超过线距的两倍2.差分对内等长误差5mil3.差分出线要尽量耦合4.走线需要优化一下5.RX和TX要创建class,进行等长处理,误差100mil6.时钟信号需要包地处理7.注意除了散热过孔其他的都可以盖油处理8.注意线

扫码关注

扫码关注