- 全部

- 默认排序

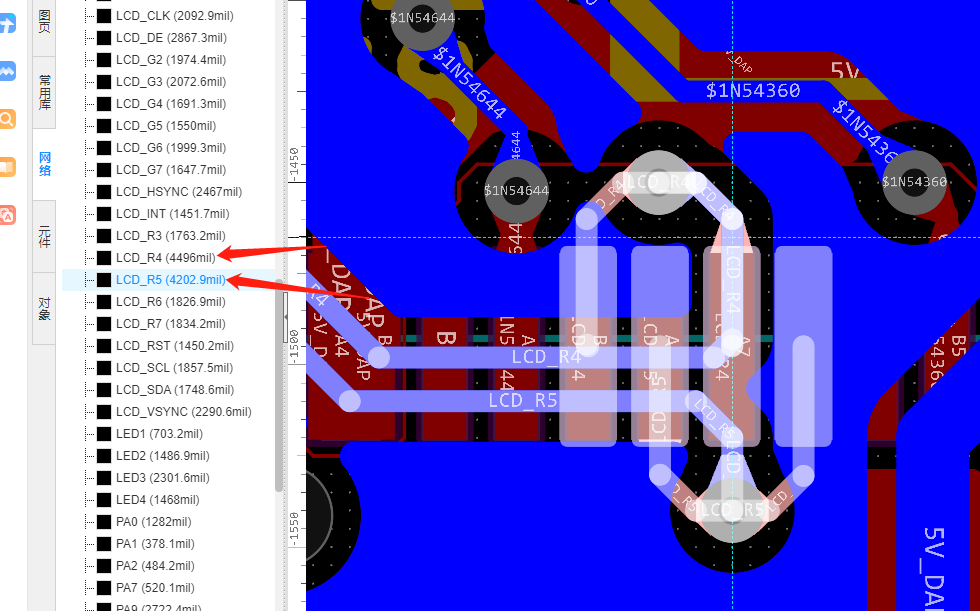

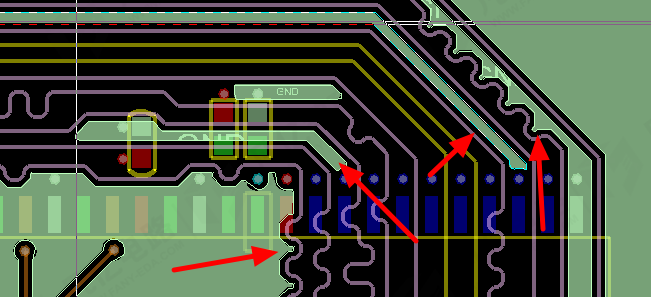

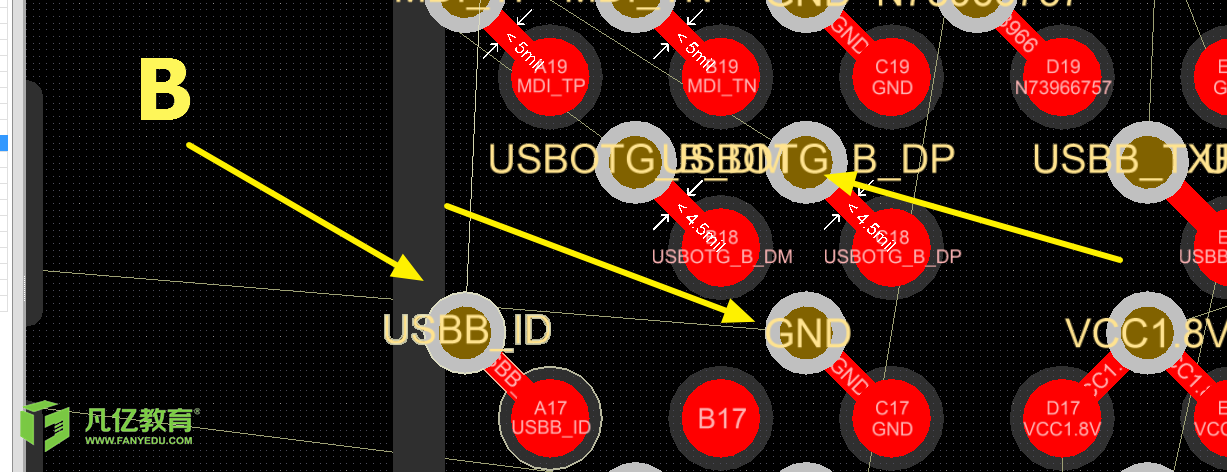

USB的差分信号需要进行对内等长,等长误差为5mil2.晶振走线需要走类差分处理3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.电源输出部

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

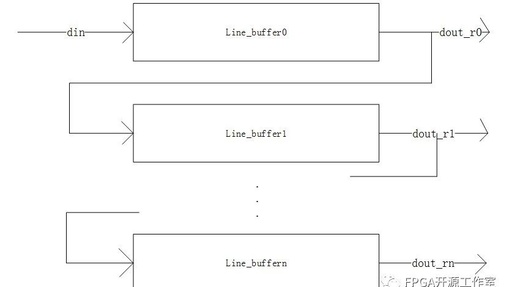

FPGA图像处理之行缓存(linebuffer)的设计一背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。FPGA实现图1 行缓存菊花链

不还是会要出现从总线上分线头出来的问题所以个人认为在非必要情况下,只要不小于90°,都是可接受的DDR3/4里面,多片FLASH,这种情况很常见

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

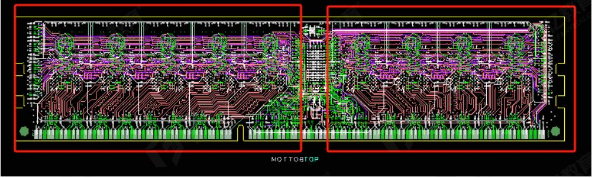

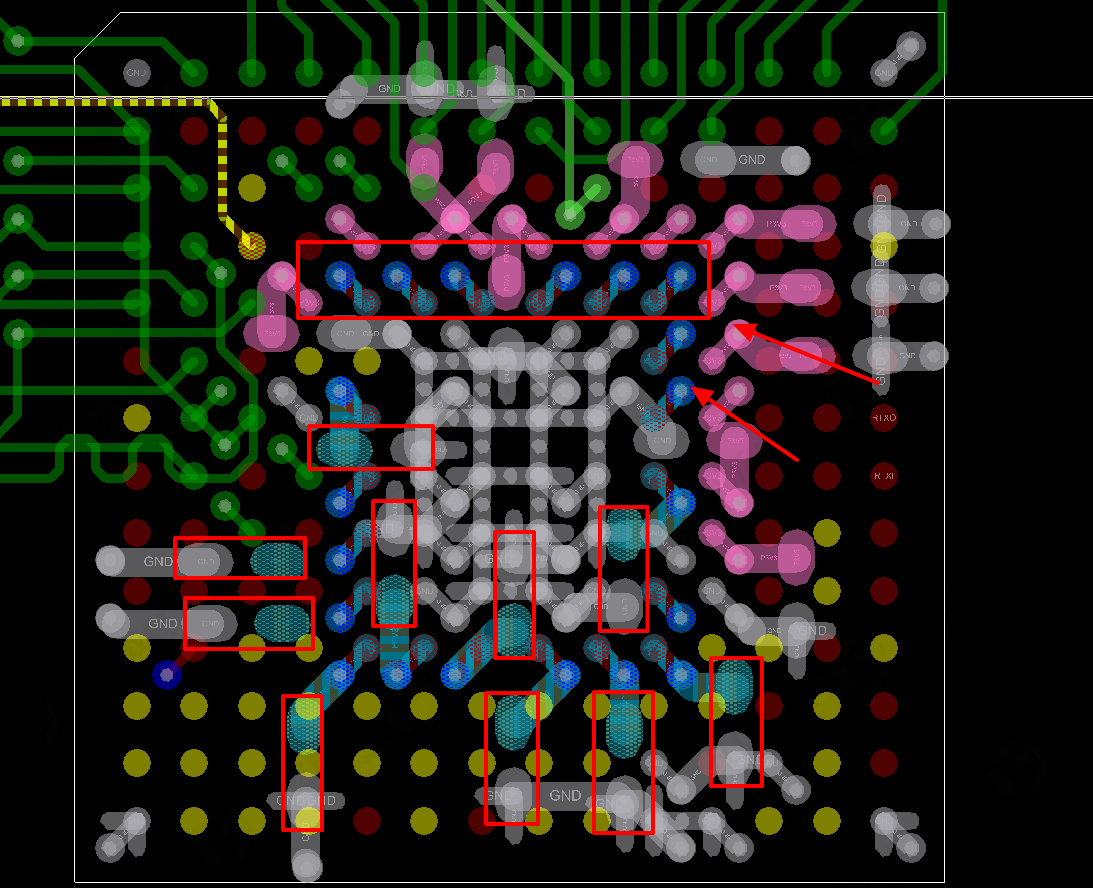

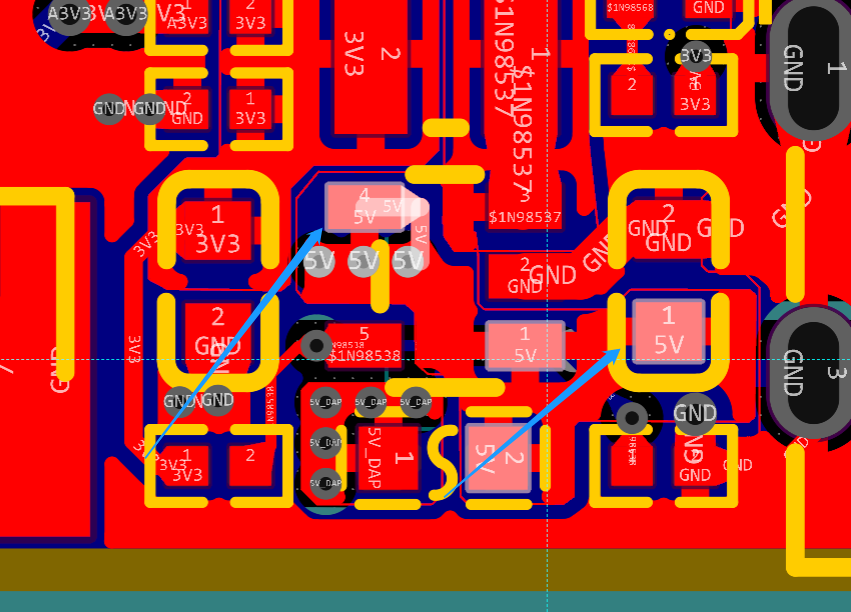

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

在规则里面这么多拓扑结构,很多时候我们只需要使用第一个shortest规则就可以,在ad中这几个出线规则其实并不需要我们去太多的纠结,因为对于器件而言不同的器件我们使用的布局方式又是不一样的,比如DDR什么时候用T点,什么时候用菊花链 ,什么时候用fly-By,等等这些,都是需要按照我们的行业规范进行布局和布线。

全站最新内容推荐

- 1AD-全能20期-SMT32-两层板-20期-杨文越

- 290天全能特训班22期-莱布尼兹的手稿 第十九次作业 SDRAM

- 3飞龙套餐allegro篇(PCB、硬件、EMC、单片机)

- 4飞龙套餐Altium Designer篇(PCB、硬件、EMC、单片机)

- 5飞龙套餐PADS篇(PCB、硬件、EMC、单片机)

- 6AD-全能21期-DM642开发板第一次作业

- 72024年中国及31省市3D打印市场分析及国家政策汇总

- 8AD- 杨皓文 第七次作业 2片SDRAM设计(菊花链)

- 990天全能特训班22期AD-沸点-2SDRAM

- 102.4GHz/6GHz Wi-Fi 带通滤波器: ACPF-7A24-TR1、ACPF-W065-TR1 产品介绍、特征及应用

扫码关注

扫码关注