- 全部

- 默认排序

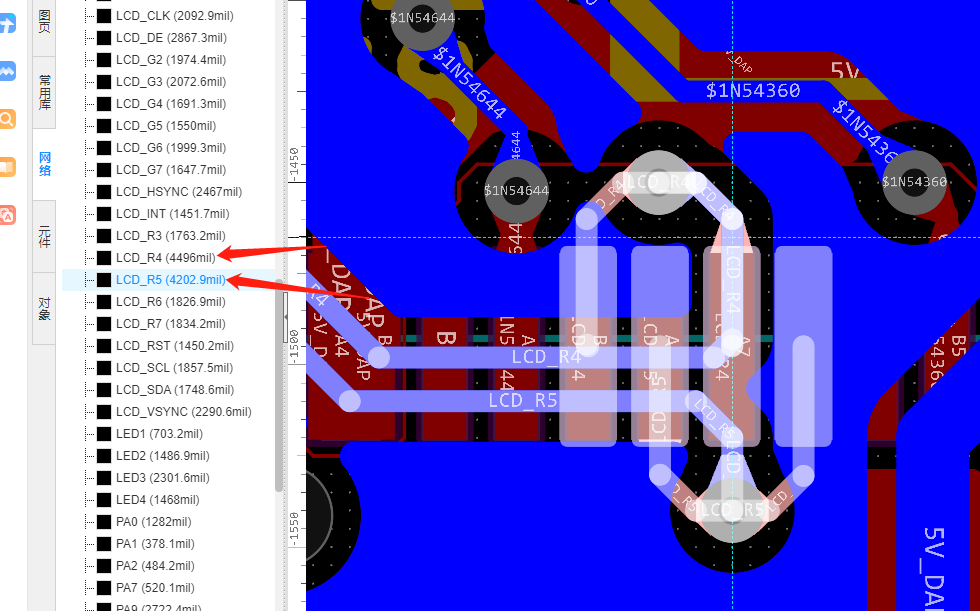

在规则里面这么多拓扑结构,很多时候我们只需要使用第一个shortest规则就可以,在ad中这几个出线规则其实并不需要我们去太多的纠结,因为对于器件而言不同的器件我们使用的布局方式又是不一样的,比如DDR什么时候用T点,什么时候用菊花链 ,什么时候用fly-By,等等这些,都是需要按照我们的行业规范进行布局和布线。

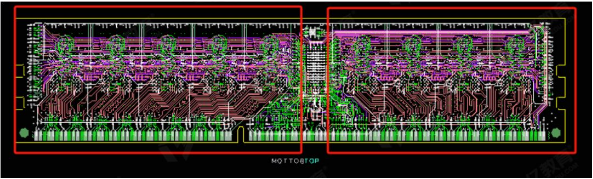

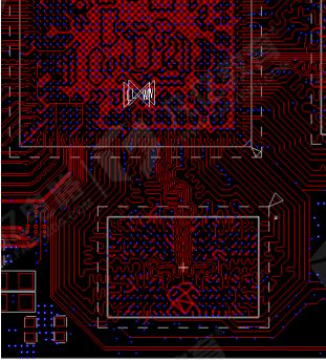

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

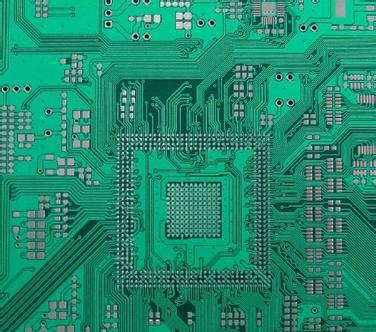

★ 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★菊花链拓扑结构的认识及设置★掌握蛇形等长走线,掌握★了解常见EMC的PCB处理方法3W规则的应用

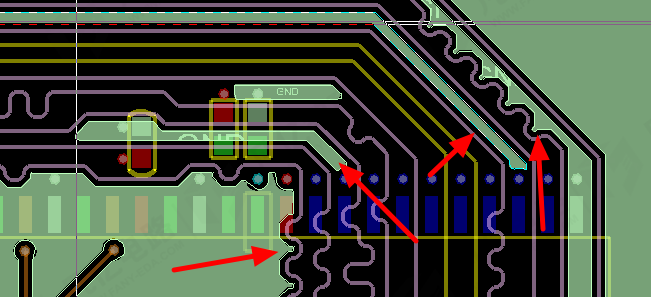

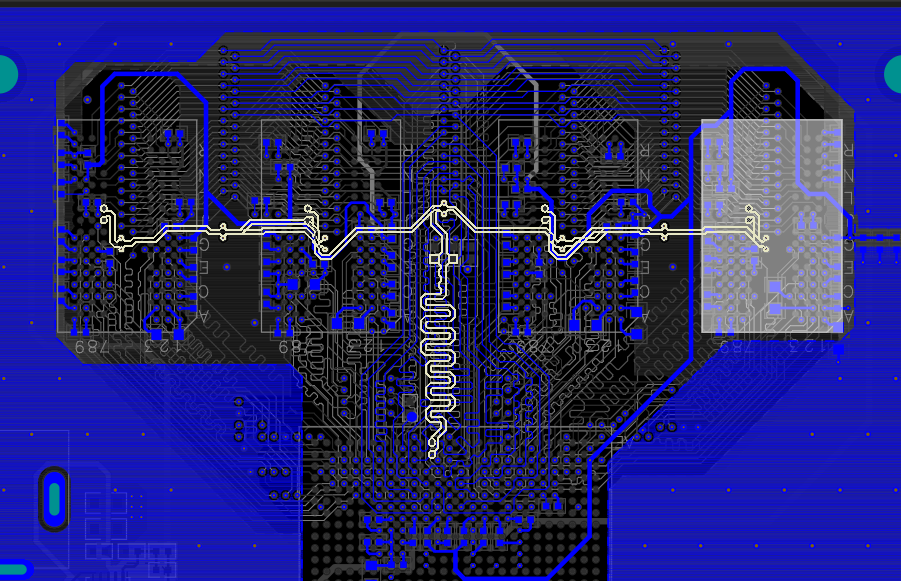

DDR3尽量采用菊花链形式,效果更加2.注意数据线之间等长需要满足3W间距规则3.注意VREF电源走线需要加粗到15mil以上,尽量不要有锐角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

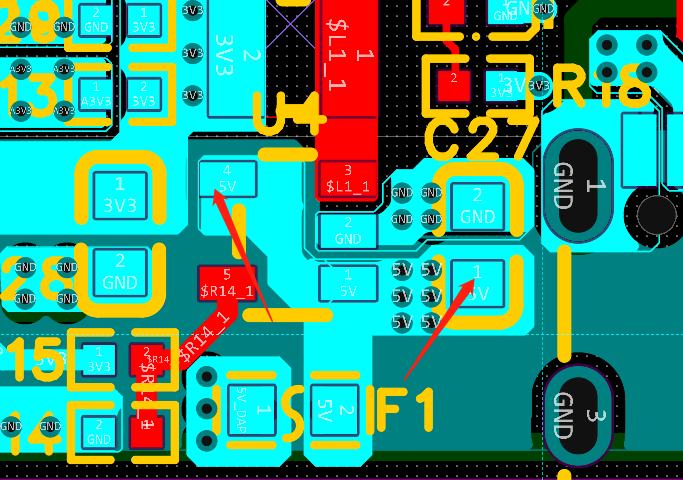

DDR采用菊花链拓扑结构时,由于信号传输线较长通常需要在DDR末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

PCB设计流程规范

直播结束后扫码添加助教领取课件直播时间:2022年12月23日 晚8点背景介绍:我们发现很多工程师在PCB设计时不够规范,从开始的布局扇孔,以及到后面规则以及布线的时候都有体现,可能后期板子上面也会因为这些因素影响板子的性能等,我们要做的就是减少这种情况的发生,在设计的时候严格按照设计规范来进行。直播能帮到用户些什么:本次直播将对PCB设计整个流程做一个介绍,从一开始的前期准备再到后面的叠层与阻抗的计算,设计规则以及布局布线等都会介绍一下一下其中的要点,可以让大家在PCB设计时更加清楚自己每个阶段需要做什么事情,怎样才能做好。直播大纲:1、PCB设计流程介绍2、PCB布局规范讲解3、PCB布线规范讲解4、PCB后期的规范处理课程主要讲了哪些知识点:1.布局前的准备,包括结构的确认,电源二叉树的分析等2.布局规范,阻抗与叠层的了解,class类的建立3.布线思路讲解,高速信号的处理4.后期PCB与Gerber文件的检查参与直播中好礼抽取5名学员赠送价值148元Altium Designer 4层菊花链核心板PCB设计教程

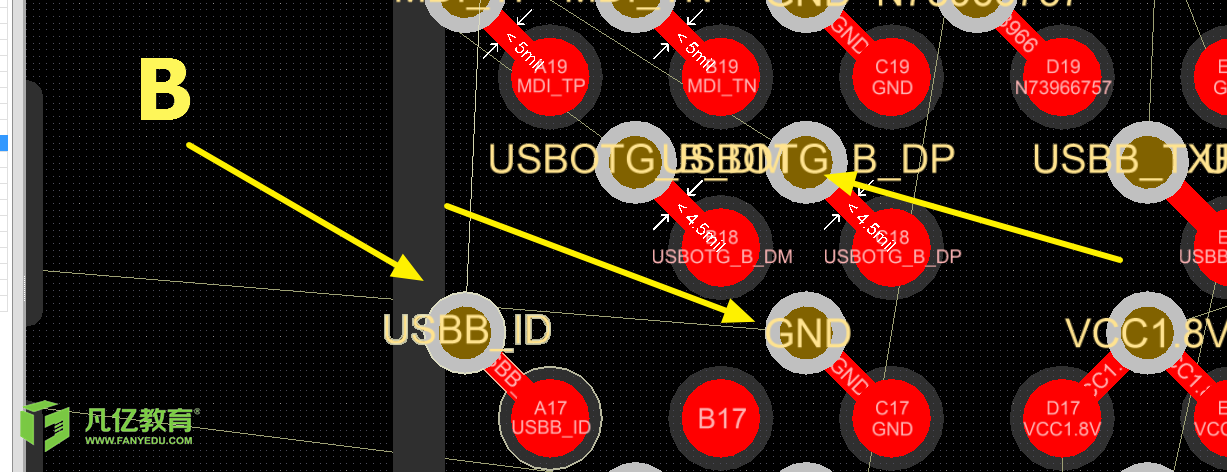

USB的差分信号需要进行对内等长,等长误差为5mil2.晶振走线需要走类差分处理3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.电源输出部

通过这一课程我能学到什么1)Allegro 4层板布局布线技巧2)Allegro 4层板TI主控设计3)Allegro软件基本操作技巧4)菊花链拓扑设计5)凡亿高手实战经验这个是一个非常经典的4层allegro达芬奇核心板设计,基于TI的主控DM642,全程讲解通过Allegro软件来设计一个4层的达芬奇开发板的PCB设计实战过程,从前期的原理图导入,导后期输出生产文件(GERBER )的全过程。

DDR拓扑结构的详细解析

在进行多片DDR设计的时候,通常DDR会存在拓扑结构,下面我们将详细介绍一下各种拓扑结构的区别以以及应用场景。首先我们先介绍一下,当只存在一片DDR的时候通常是采用点对点的连接方式,点对点的布线方式优点是结构简单,阻抗以及时序容易控制,适合

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.差分走线要尽量耦合出线,满足差分间距规则3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.器件摆放尽量对齐处理5.pcb上存在开路现象6

扫码关注

扫码关注