- 全部

- 默认排序

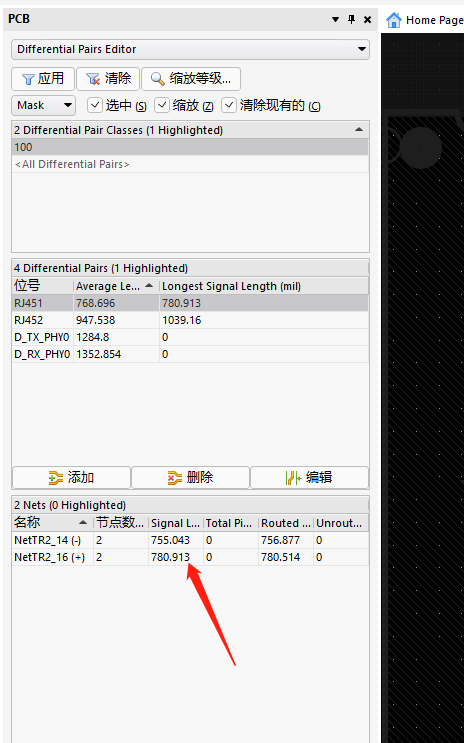

差分线单独拉等长不能拉,我是改别人画的PCB,以前人用的7mil的线宽 我改成5.6mil了 然后在做等长的时候就不能做 ,如果我将线在改成7mil就又可以了,(以前人规则里面没什么设置 只是简单设置了一下线宽线距而已) 在线等 谢谢!!! 373064203 我扣扣 我可以给发源文件 帮忙解决

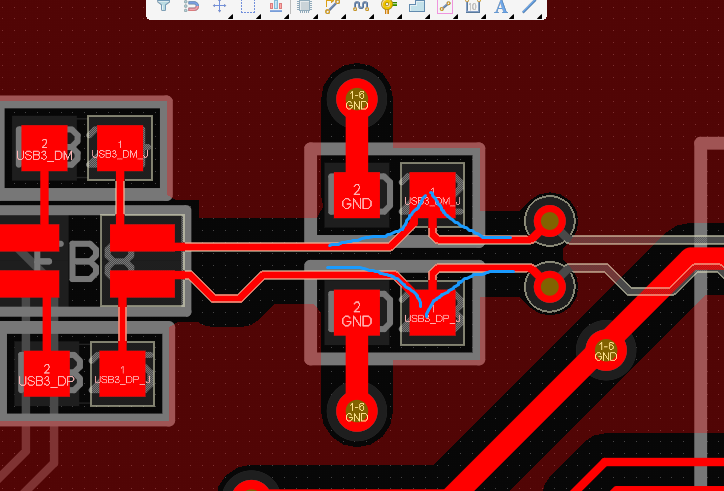

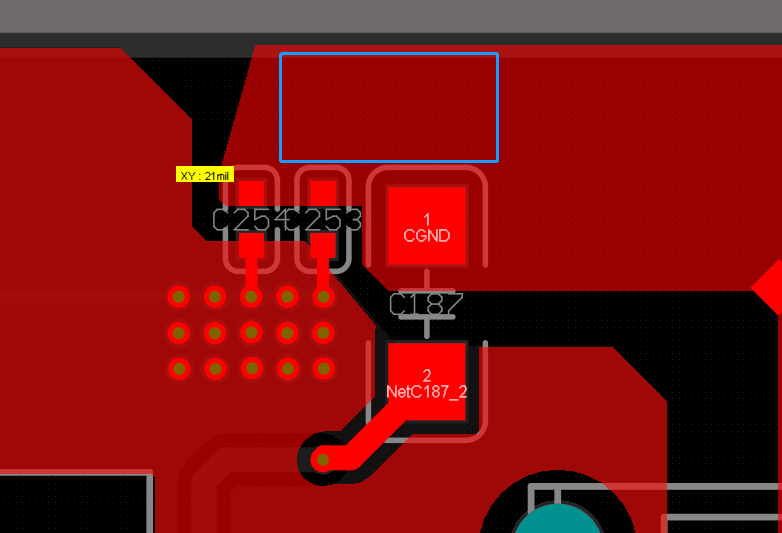

焊盘出线需要优化一下2.铜皮需要优化一下,尽量不要直角,建议45度3.差分走线需要耦合,后期自己调整一下4.差分对内等长误差5mil所有差分对都要注意一下5.负片层需要指定网络进行连接6.差分走线需要按照阻抗线宽线距进行走线,避免发生阻抗突

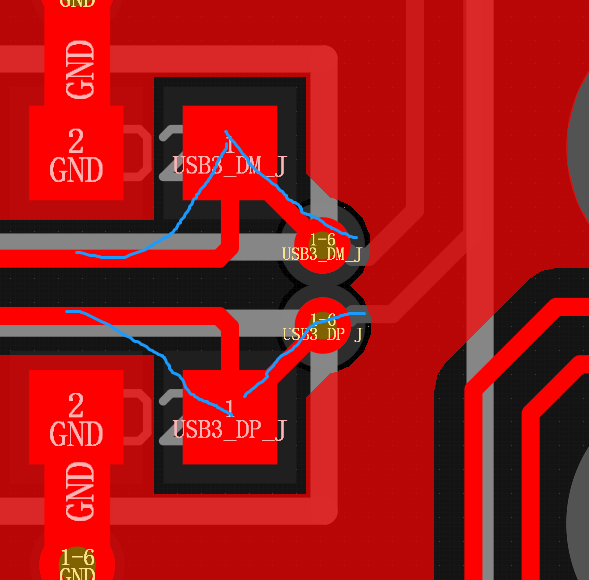

注意焊盘出线规范后期自己优化一下2.差分对内等长凸起高度不能超过线距的两倍3.注意差分走线要尽量耦合4.一层连接不用打孔,注意不要出现STUB线头5.CC1和CC2属于重要信号,走线需要加粗6.注意差分信号包地要在地线上打上地过孔7.过孔需

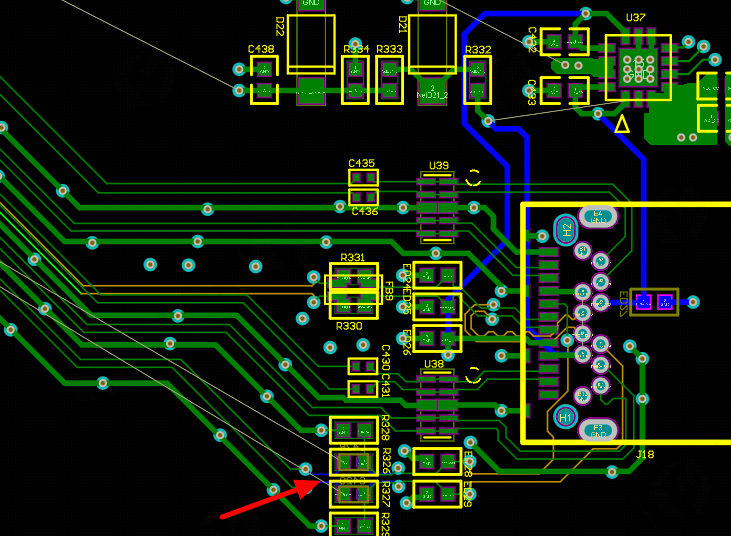

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处drc7.时钟信号包地,尽量

多处飞线未连接差分出焊盘后尽快耦合差分对内绕线不符合规范存在报错未处理差分走线不耦合,前后前后线距不一致兼容器件这样布局差分对内等长控制5mil误差,有两对差分走线没有建立差分对,没有加入差分组以上评审报告来源于凡亿教育90天高速PCB特训

跨接器件旁边尽量多打地过孔2.焊盘出线需要优化一下3.差分走线不满足阻抗线距规则4.晶振下面不要放置器件和走线,包地需要在地线上打过孔5.注意打孔尽量不要打在焊盘中心6.走线一层连通,不用打孔7.走线需要优化一下,尽量45度8.RX等长误差

扫码关注

扫码关注