- 全部

- 默认排序

穿插讲述了Cadence17.4原理图工具的使用方法和GD32E230硬件设计外围电路配置方法,各种常用芯片的使用等内容。力增用一个从无到有的设计方式,从原理图的设计构思开始,通过视频的方式带领大家从原理图设计到错误检查,网络表生产,封装库制作,同步进入PCB,3D模型制作,布局,规则,布线,文件输出的操作全流程和设计方法等经典操作。

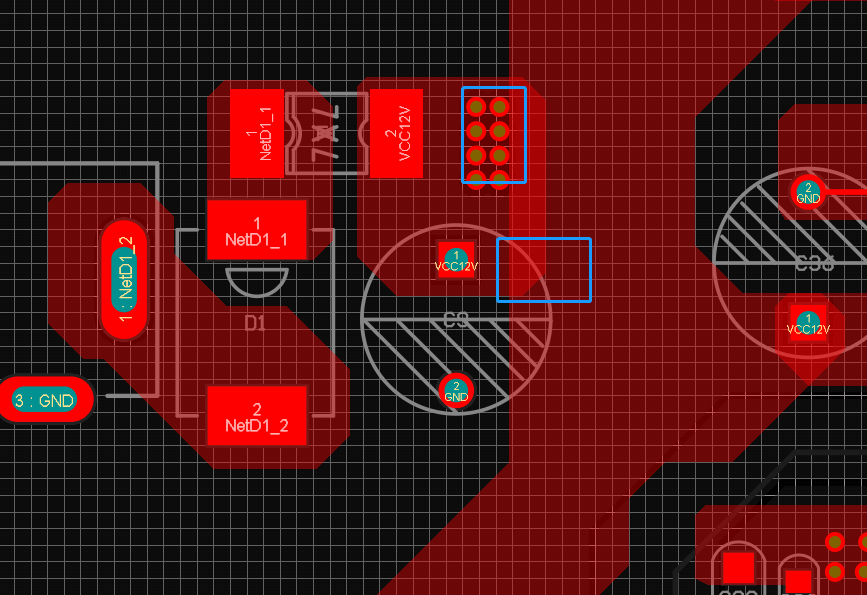

输出打孔要打在电容后面输入电容要靠近管脚摆放,越近越好,尽量少打孔后期自己调整一下布局3.布局需要优化一下,尽量紧凑,器件中心对齐,更美观4.有多余的焊盘5.输入地和输出地尽量连接在芯片中间进行回流6.注意焊盘出线规范7.散热焊盘中间需要打

变压器上除了差分信号,其他的加粗20MIL走线:晶振尽量包地处理:RX TX以及差分组内等长没啥问题:建议机壳地与电路地之间分割2MM间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

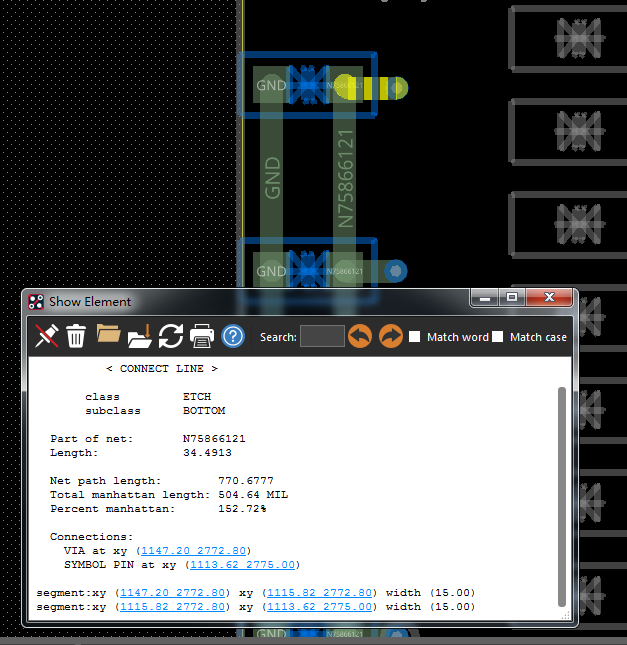

此处不满足载流,后期自己铺铜处理一下,走线最少需要加粗到15mil以上载流计算都是以最窄处计算的2.注意数据线,地址线之间等长需要满足3W规则后期自己优化一下3.像此处的碎铜尽量挖空处理注意差分对内等长误差5mil其他没什么问题以上评审报告

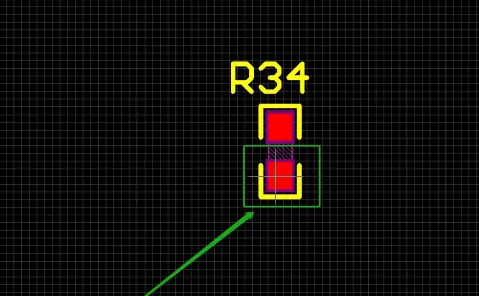

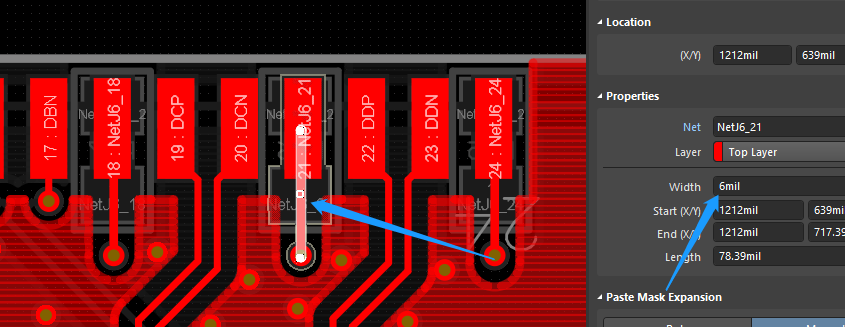

在电子工程领域,很多电子工程师经常使用Altium Designer(简称:AD)软件来捕捉元器件中心位置的,这种操作对于提高设计效率和确保设计质量非常重要,可以更精确定位元器件,减少布局布线的工作量,提高设计的可维护性,那么如何操作?1、

网口除差分信号外,其他的都需要加粗到20mil2.跨接器件旁边要尽量多打地过孔,间距要保证2mm,有器件的地方可以不满足3.此处的孤岛铜可以挖掉4.TX和RX等长误差100mil 5.差分信号需要走内差分处理,包地要包全6.焊盘出线不规范,

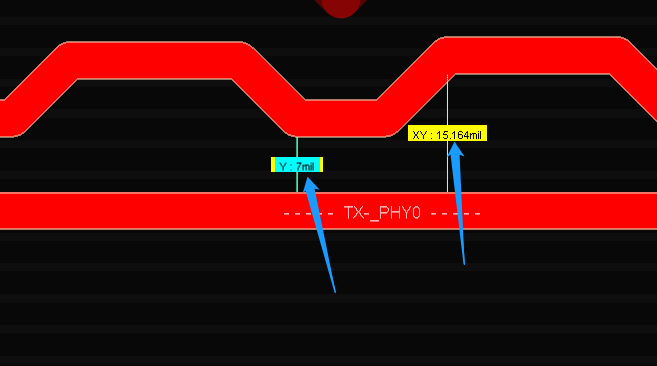

差分线等长不符合规范,锯齿状等长不能超过线距的两倍2.差分走线尽量耦合3.电源线宽尽量保持一致,满足载流4.中间的焊盘可以多打过孔5.存在无网络过孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

扫码关注

扫码关注