- 全部

- 默认排序

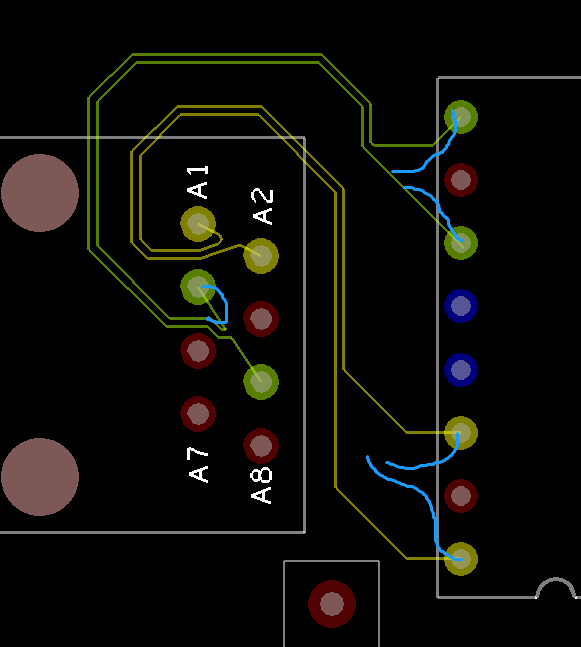

差分走线需要再优化一下2.此处差分尽量打孔换层,在旁边添加一对回流地过孔,包地即可3.电容靠近管脚放置,走线优化一下,不要有锐角4.焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.存在多处开路6.差分需要进行对内等长,误差5mil7.R

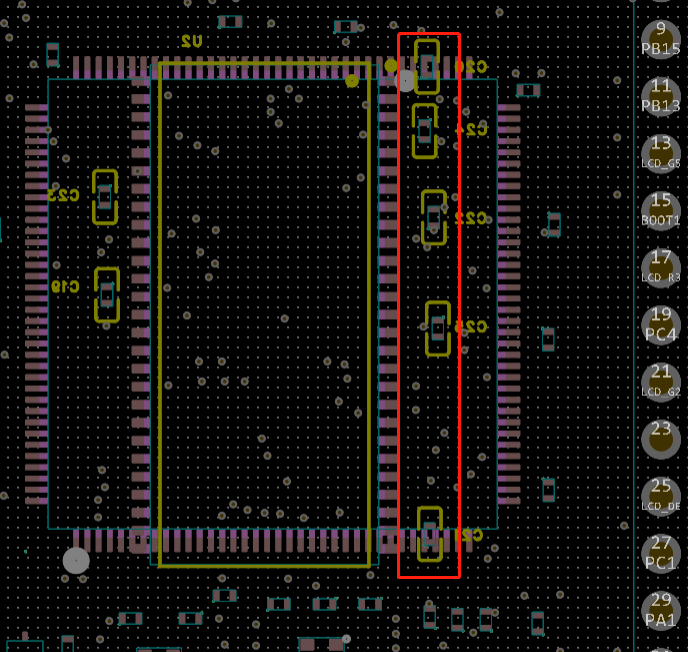

差分对内等长误差5mil2.晶振需要包地处理3.SD卡信号线需要等长处理,误差300mil4.滤波电容靠近管脚放置,保证一个管脚一个以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

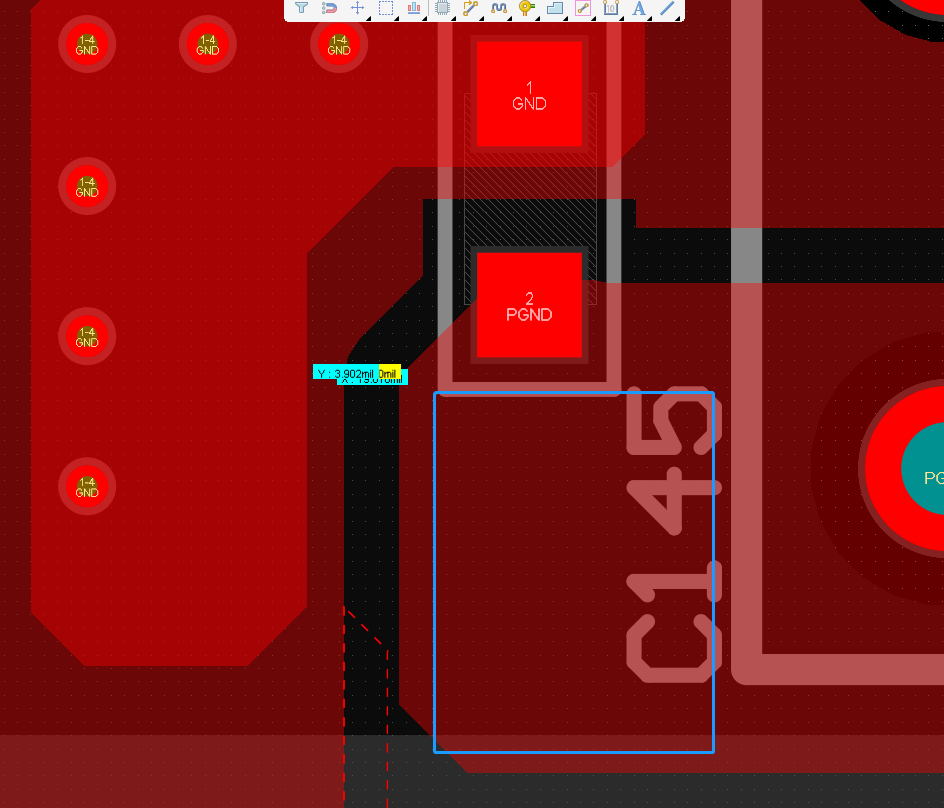

跨接电容旁边进行多打地过孔,不同的地间距建议2mm2.器件干涉3.SDRAM等长还存在没有达到目标值4.走线尽量不要从电阻电容中间穿5.滤波电容应该靠近输入管脚放置以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

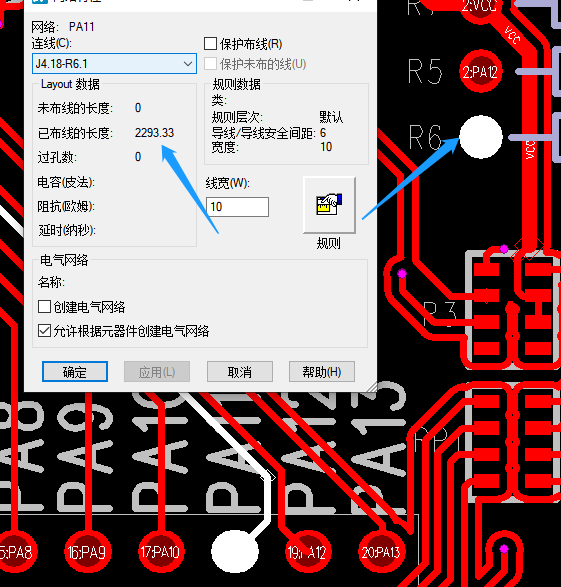

器件摆放注意局部对齐处理2.注意器件干涉3.电源输出的滤波电容要靠近输出管脚放置4.电源输入输出换层打孔处理不当,输入应该打在滤波电容的前面,输出打在滤波电容的后面5..差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍6.确认一下此处

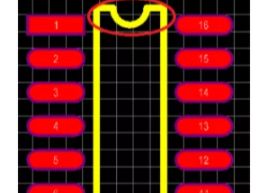

1.IC芯片类比如单片机,74LS138等此类芯片的特点就是管脚众多,多呈对称式分布,例如以下以SO-16为例,如下图所示为其封装:此类的IC芯片会有一个圆角标识1脚,如上述图中的红圈所标识的地方即可SO-16芯片的1脚,可以看到如下SO-

针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称Name以及管脚编号Numbers先按数字1、2、3...,一

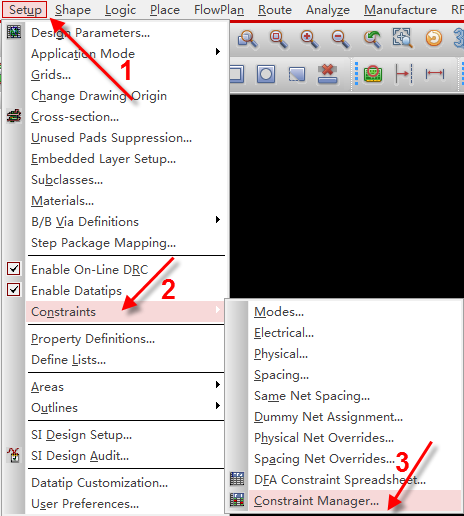

答:我们在Allegro软件中,不论是做绝对传输延迟还是做相对传输延迟,从所有的等长列表中可以看到,它的本质都是从一个元器件的管脚连接到另一个管脚的长度,也就是我们所说的Pin-Pair到Pin-Pair的长度。我们创建等长集合,其实也是创建Pin-Pair的集合,这里,讲解一下,Allegro软件中如何创建Pin-Pair,具体操作如下:

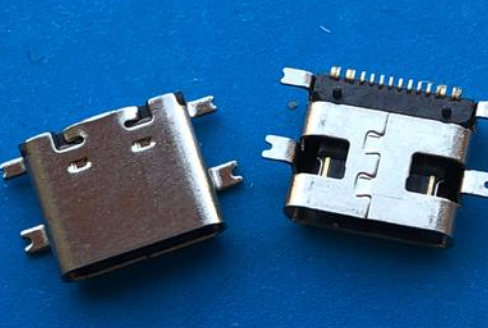

答:根据器件规格书(Datasheet)制作封装时,一般做出来的封装焊盘管脚长度需要做适当的补偿,即适量地对器件原先的管脚加长一点,具体的补偿方法,是根据器件的管脚类型来补偿的,可按以下办法:第一类,无引脚延伸型SMD封装,如图4-100所示: 图4-100 无引脚延伸型SMD封装示意图A—零件实体长度 X—补偿后焊盘长度 H—零件脚可焊接高度

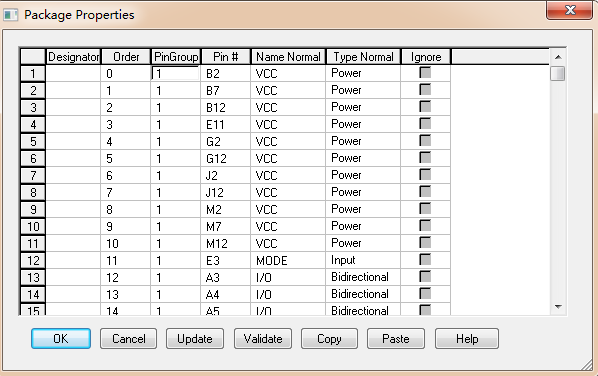

答:Pin Group这个属性是指可以交换的属性设置,我们删除这个属性的操作如下;第一步,打开库文件,点击菜单View→Package,进入到整个器件的编辑属性,然后点击菜单Edit→Properties,或者按快捷键Ctrl+E,进入器件管脚属性编辑页面,如图2-92所示: 图2-92 编辑器件属性示意图第二步,在弹出的器件属性框找到Pin Group这一栏,Pin Group这一栏中定义了数值,数值相同的就是可以进行管脚交换的,如图2-93所示; 图2-93&n

答:orcad创建封装库时,放置管脚的Type的含义是管脚的类型,表示管脚的类型,每一种类型的含义解释如下:3 State:三态类型,0与1与高阻态,一般用于逻辑门器件;Bidrectional:双向传输类型,一般用于DC-DC电路器件;Input:输入信号,一般用于IC类器件的输入管脚;Open Collector:表示开集电集,一般用于三极管或者是MOS管;Open Emitter:表示开发射集,一般用于三极管或者是MOS管;Output:输出信号,一般用于IC类器件的输出管脚;Passiv

扫码关注

扫码关注