- 全部

- 默认排序

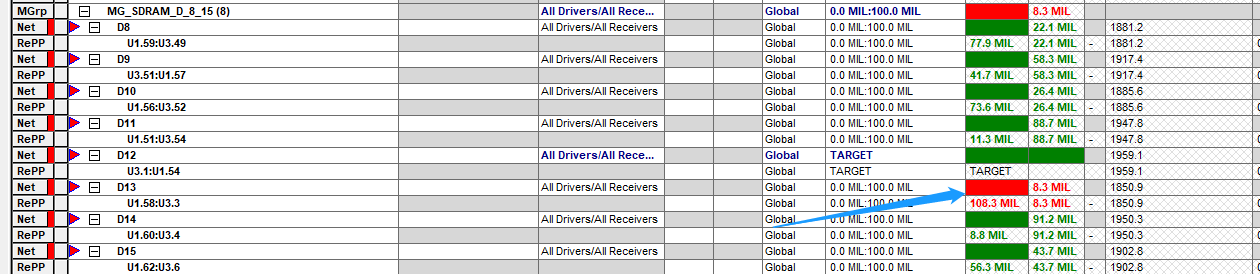

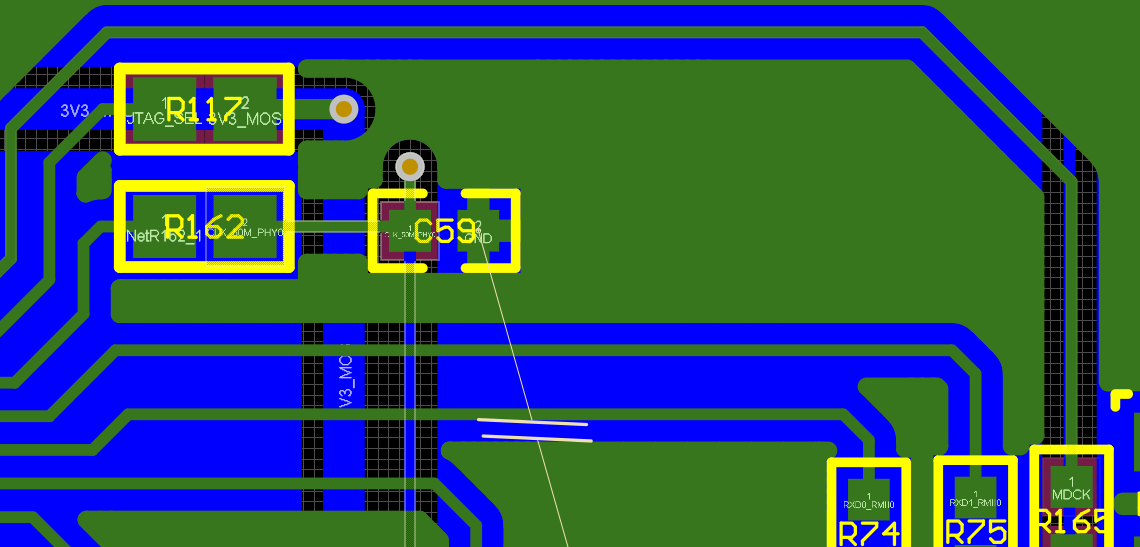

1SDRAM注意数据线等长存在报错2DDR注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

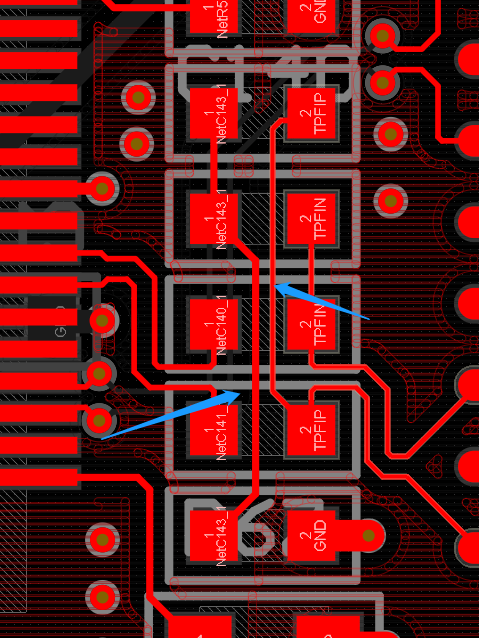

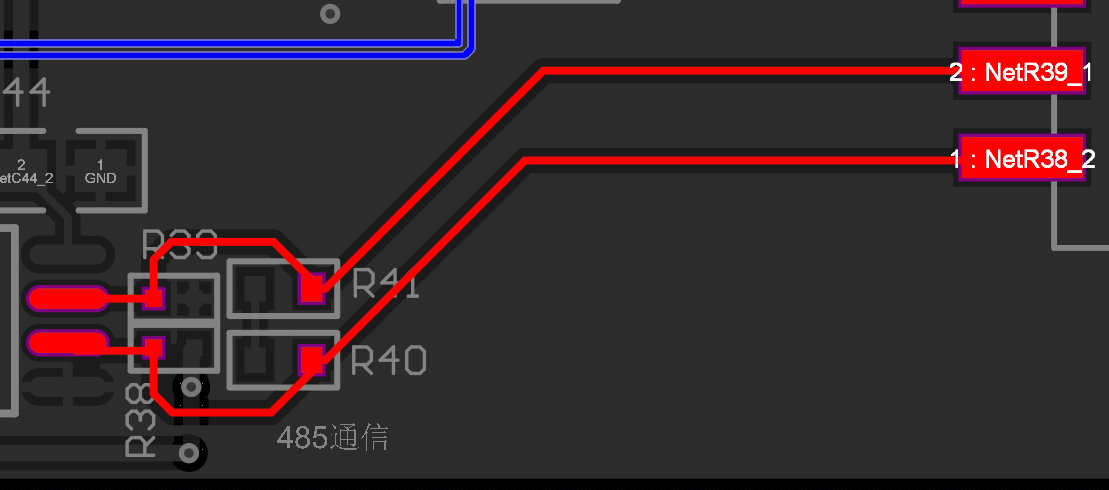

走线不要从电阻电容中间穿,后期容易造成短路,可以打孔走底层2.跨接器件旁边尽量多打地过孔3.数据线和地址线等长都需要满足3W4.电感下面尽量不要走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

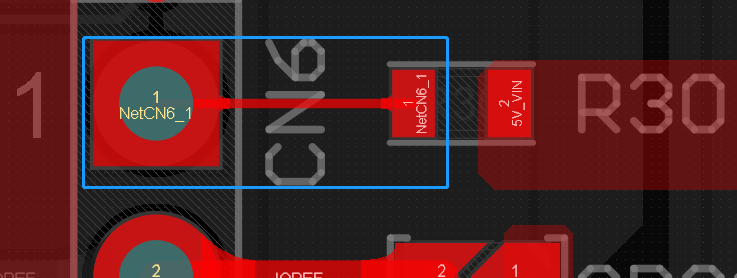

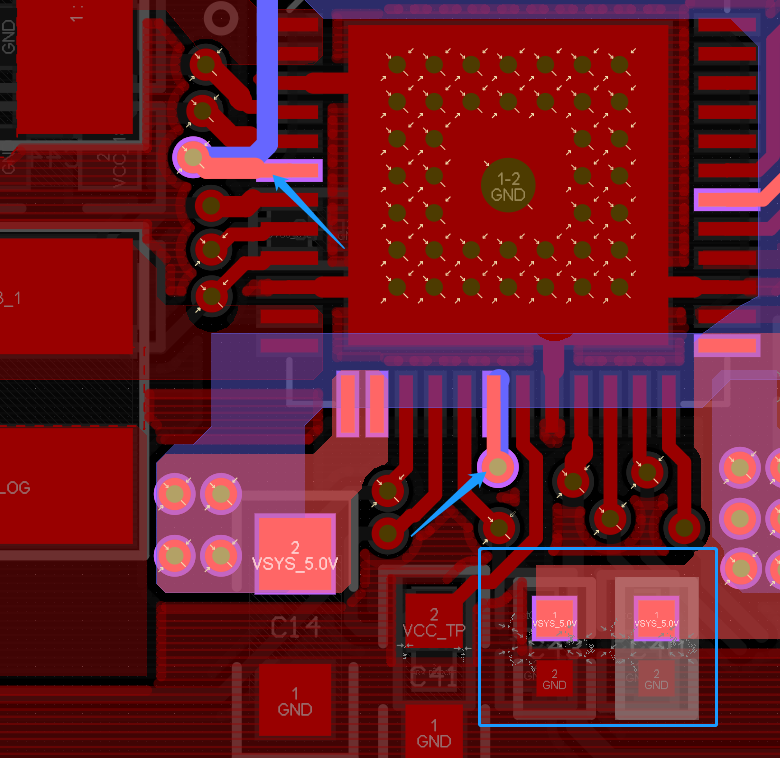

电源输入不满足载流,加粗走线或者铺铜处理2.电源输出滤波电容按照先大后小的顺序摆放3.注意满足载流4.电源输入尽量铺铜处理,先经过滤波电容在进入到管脚5.输出滤波电容按照先大后小的顺序靠近管脚进行摆放6.晶振下面不要走线7.电源管脚走线都需

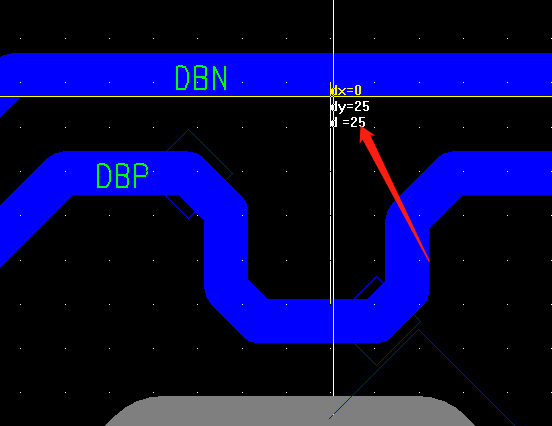

我们平时在PCB布线的时候,对于比较重要的信号都要做特殊处理,比如包地或者时“3W”,所谓3w指的是线与线之间的间距要满足三倍的线宽,那么我们怎么理解这个3W原则呢,他是如何降低信号之间的串扰的呢?我们要了解这个原因可以先了解电容的概念,电

1.存在开路,孤岛铜皮没有连接出去。2.芯片中间过孔没有连接出去导致天线报错。3.多处孤岛铜皮和尖岬铜皮。4.电容地网络要和电源一样加宽载流。5.差分焊盘出线尽量耦合6.差分走线不耦合7.时钟信号走线要包地处理8.走线尽量短9.TX、RX没

锯齿状等长不能超过线距的两倍2.差分出线需要优化一下3.滤波电容放置有问题,有网络没有导入成功4.这几个应该是一个网络,滤波电容靠近对应的管脚放置5.器件摆放不要挡住一脚标识6.TX和RX要添加等长组分别进行等长,误差100mil7.存在s

滤波电容放置尽量靠近管脚放置2.挖空后需要右键重新铺铜才有作用3.此处不满足载流4.电感下面尽量不要放置器件5.走线未连接到焊盘,存在开路6.铺铜尽量把焊盘包裹起来7.走线需要优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

五串BMS-2版公益评审

差分线不耦合,间距也不一致差分对内不等长误差应控制在+-5mil焊盘出线不规范不要从焊盘中间出线散热过孔应该做开窗处理晶振包地要包全上面部分也要包进去确认这些地方走线是否满足载流要求输出电容要按照先大后下的顺序排列输入端电容应靠近管脚放置c

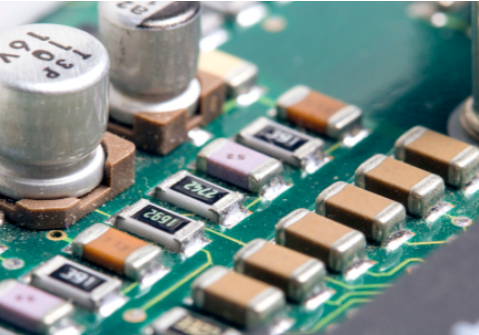

不懂硬件的人,会觉得硬件高深莫测,“为什么他改几个电阻、电容就调出来,我弄个半天没搞定?”,“噢,靠的是经验”,但是经验又是什么呢?不能形容,反正就是不明觉厉。就是这种崇拜心理,才能触发你的好奇心,去学下去,这也是成为工程师的首要条件,但这

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC

扫码关注

扫码关注