- 全部

- 默认排序

随着芯片产业的迅速发展,芯片间数据交换也在成倍增长,传统的芯片封装方式几不能满足巨大的数据处理需求。同时,随着芯片制造逐渐进入摩尔定律的无理极限,芯片制程工艺提升放缓,以3D堆叠封装为代表的先进封装技术即将成为未来的重要发展方向。以苹果为例

众所周知,随着电子电路逐渐小型化、智能化,摩尔定律即将达到物理极限,也就意味着芯片性能很难再有极大的提升,这也是近年来台积电三星等半导体厂商的先进制程性能提升不再那么多的原因。要解决这个方法,关键在于量子计算机。近日,来自澳大利亚悉尼的工程

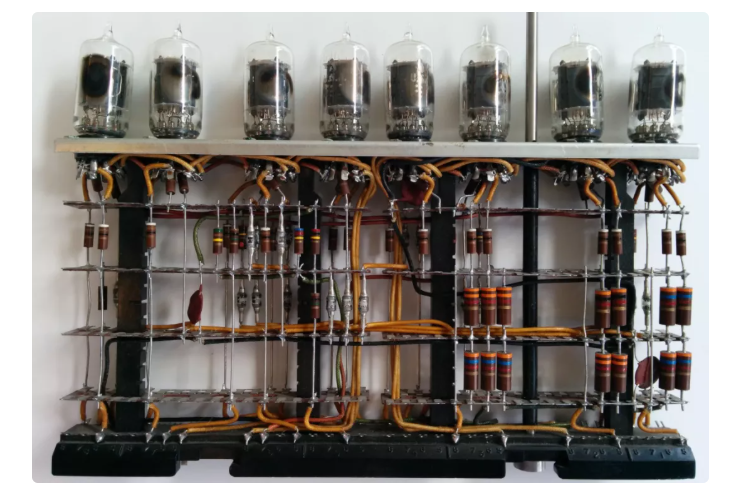

随着集成电路技术沿摩尔定律发展至今,从第一代插孔元件、第二代表面贴装、第三代面积阵列,再到现在的芯片封装,这些封装技术以系统级封装技术(SIP)的实现奠定了基础,然而很少工程师知道,良好的SIP可明显改善电磁兼容和信号完整性问题。所谓的系统

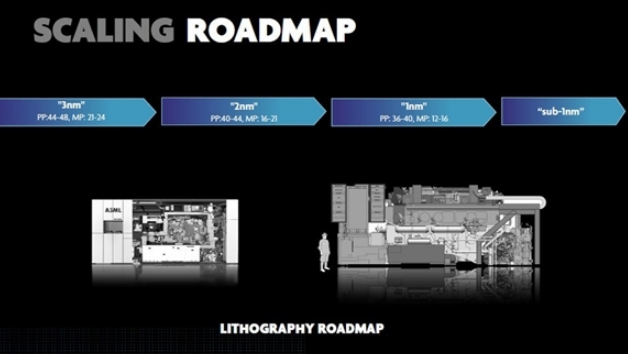

随着时代高速发展,芯片迭代更新速度大大加快,目前已发展至3nm先进制程工艺,虽然仅有台积电和三星电子目前能制造出,但根据摩尔定律,有很多人在猜测2nm芯片何时出?据媒体报道,台积电即将敲定其未来3nm和2nm支撑客户,除了众所周知的苹果之外

近期看到Robin Kearey的一篇博文 SMALLER IS SOMETIMES BETTER: WHY ELECTRONIC COMPONENTS ARE SO TINY[1] ,详细分析了电子器件的微型化所带来的影响。如果你还在想疯狂压缩电路体积的话,看看他的分析也许会让你冷静下来。

全球唯有台积电和三星能够制作5nm以下工艺的晶圆代工,然而随着芯片工艺制程的提升,研发难度越来越高,发布时间也越来越少,这也造成很多人说摩尔定律将死。纵观台积电的路线发展图,台积电将在2022年年底量产3nm工艺,2025年量产2nm,在此

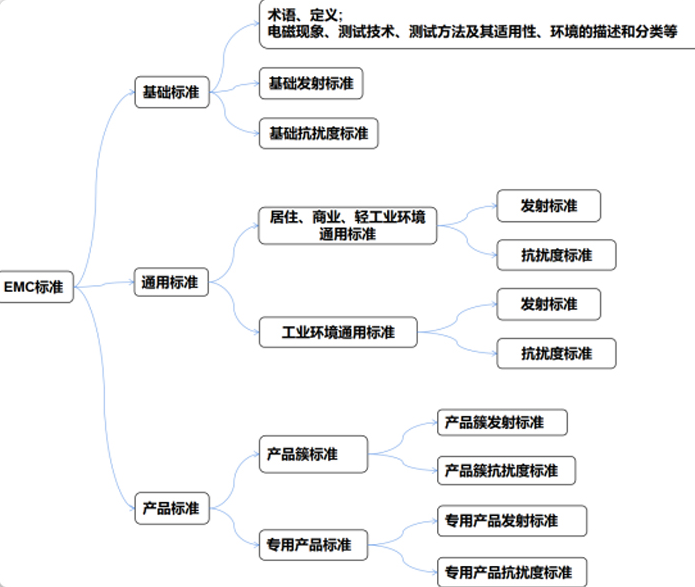

随着摩尔定律的提出,电子产品的性能不断的翻倍上涨,电磁兼容性(EMC)问题已成为电子产品性能提升的首要障碍问题,这也促使大多数电子工程师不得不拥有EMC电路设计能力,所以本文将分享电磁兼容设计的基本原则及高级技巧,希望对小伙伴们有所帮助。电

众所周知,芯片的研发规律主要遵循摩尔定律,也就是每18个月到两年间,芯片的性能将翻倍增长,但由于随着芯片先进制程的提升,芯片难以达到极限,遇到技术瓶颈,所以很多人认为基于磁性材料发展建立的自旋电子学以及磁子电子学,有望帮助芯片突破物理极限。

熟悉半导体行业的人想必对摩尔定律很熟悉,摩尔定律自问世以来就是半导体行业的最高目标,正是基于该目标,电子设备变得更加快速、高效且便宜,然而随着集成电路的尺寸越来越小,摩尔定律逐渐难以实现,因此很多人声称:摩尔定律已死。摩尔定律简单来说是一个

随着科技快速发展,集成电路逐渐从小型化、智能化、功能化方面发展,芯片内置的晶体管数量也开始翻倍增长,目前数量高达几百亿以上,高速度的增长必然将达到摩尔定律的物理极限,业界人士认为量子集成电路是最有效最快速的解决方法,但由于技术限制,至今仍未

扫码关注

扫码关注