- 全部

- 默认排序

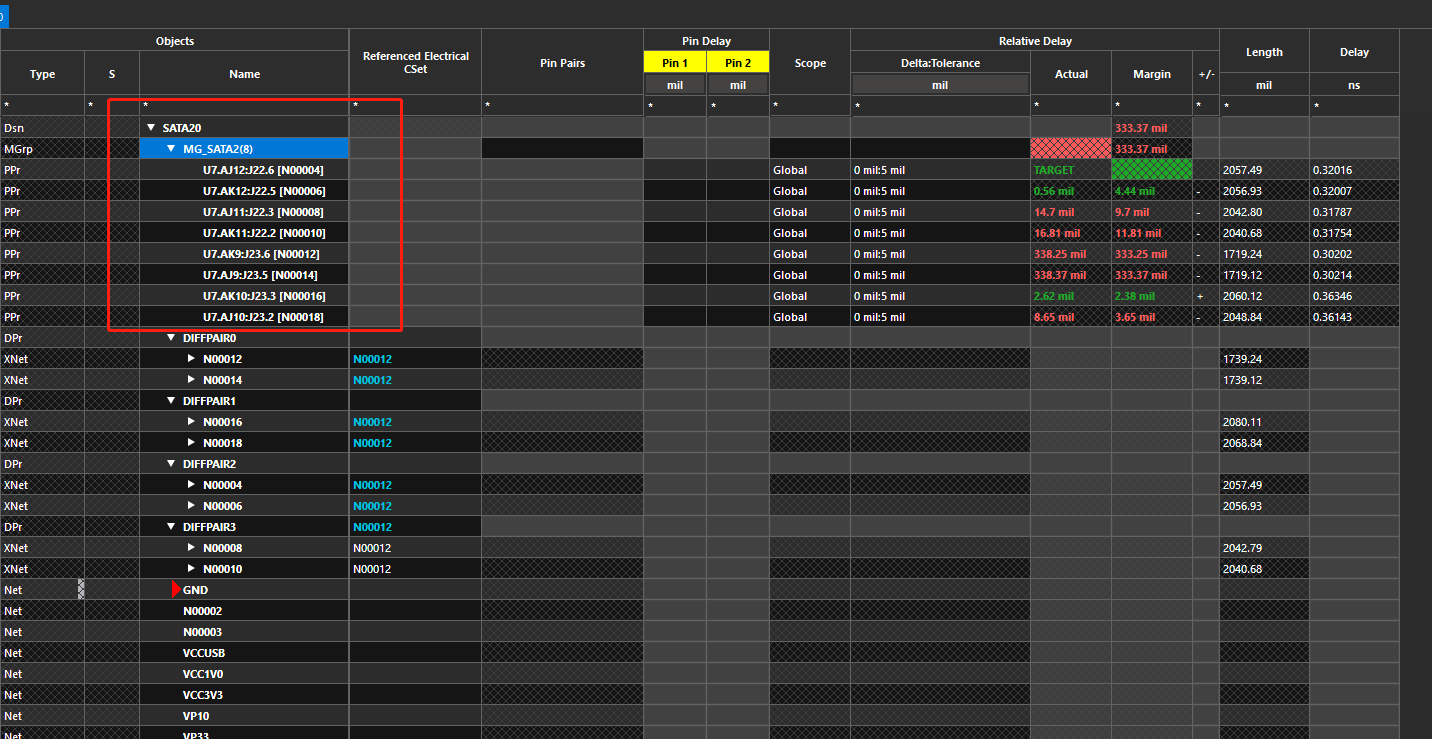

差分线对内等长误差5mil,同一组差分误差5mil规则要分开进行设置,后期自己处理一下2.焊盘出线不要走直角3.差分对内等长尽量在不耦合处进行等长4.注意器件摆放不要超出板框5.差分走线要耦合走,后期自己优化一下6.后期自己在地平面铺铜,把

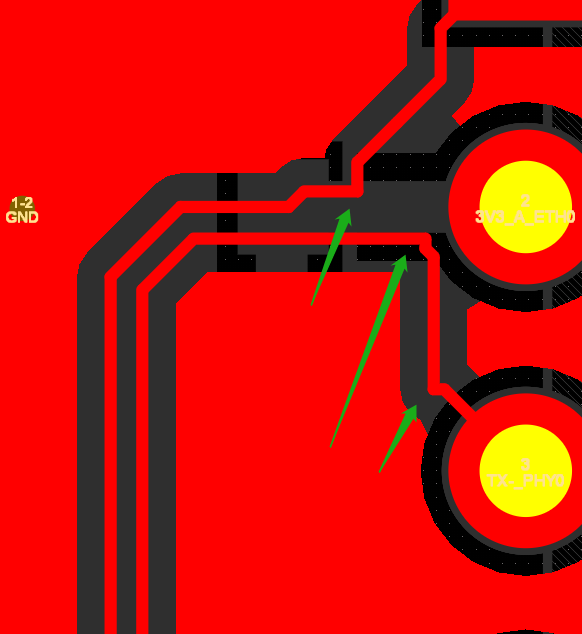

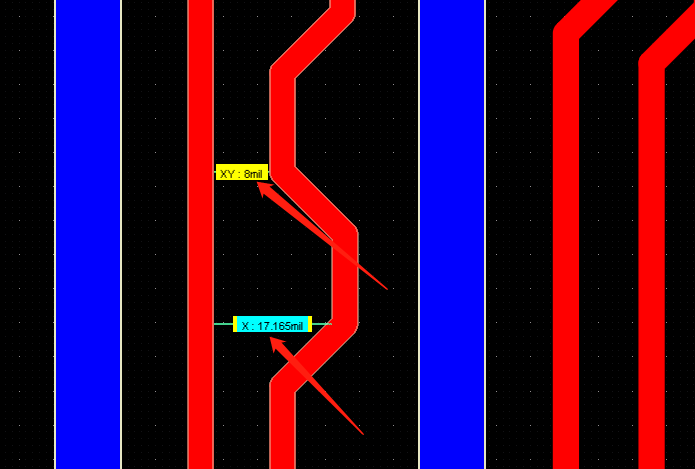

差分线都不合格,都存在直角:完全是不允许的,需要删除重新走线。上面那组差分出现,需要跟下面那组一样,下面的差分是完全合格的耦合走线:焊盘不能随意出现,需要从中心往两长边拉线:差分对内等长误差为5MIL:单端线等长改下等长模式,也是不能直角:

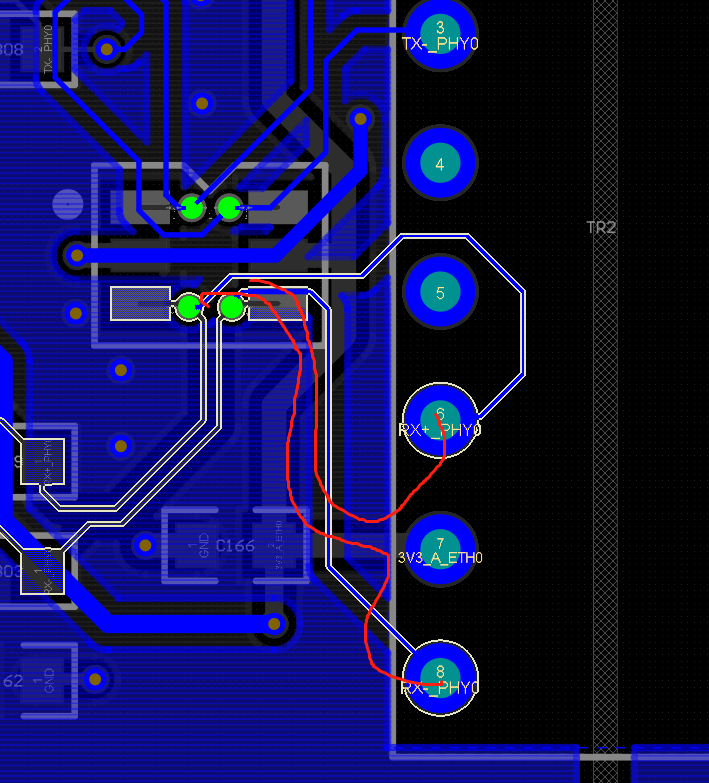

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

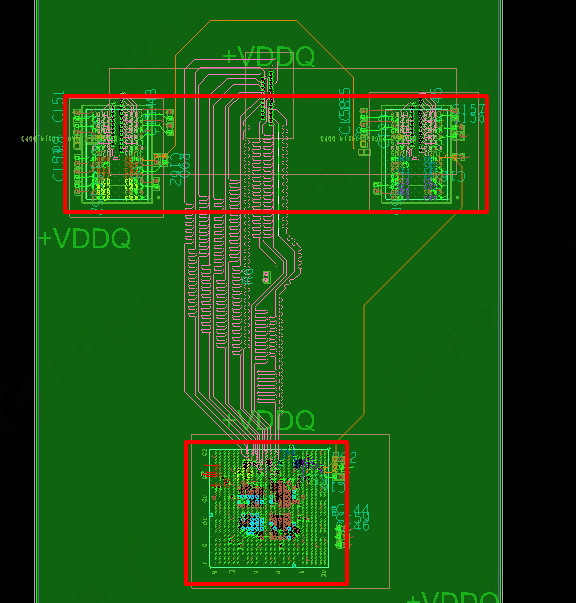

ddr之间ddr和芯片距离太远,ddr到芯片推荐600-800mil器件摆放太近丝印干涉,滤波电容推荐摆放到ddr背面靠近焊盘放置 过孔上焊盘,小器件焊盘尽量不要打孔到焊盘上差分线是主要时钟信号,尽量缩短走线电容靠近ddr中间放置差分线等长

差分线对内等长凸起高度不能超过线距的两倍2.存在开路3.注意差分需要进行对内等长,误差5mil4.注意等长尽量不要直角,建议钝角,后期自己优化一下5.后期自己在地平面和电源平面指定网络进行连接6.差分需要按照阻抗线距走,后期自己注意一下以上

这对信号也是差分对,要差分布线器件尽量靠近管脚放置,要在电容旁边打孔器件中心对齐,相邻器件尽量朝一个方向放置差分对内等长错误差分尽量靠近引起不等长端进行绕线差分包地有空间尽量包完整走线尽量不要绕线,差分线两根尽量一样长不同网络走线用同一个过

扫码关注

扫码关注