- 全部

- 默认排序

请教个问题,我AD18的库里的元器件放置在PCB时,焊盘和丝印层不是一个层,一个TOP,一个BOTTOM,封装库的元器件打开又都是对的,怎么解决

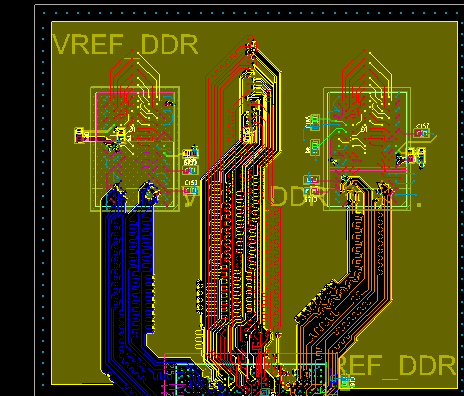

这个vref是参考电压,写入或读取数据时需要用vref来确定是高电平还是低电平,不要大面积铺铜。四块的也是一样ddr到芯片的距离有点远了一般是600-800mil丝印位置可以调一下,调整齐不放焊盘上其他的没什么问题以上评审报告来源于凡亿教育

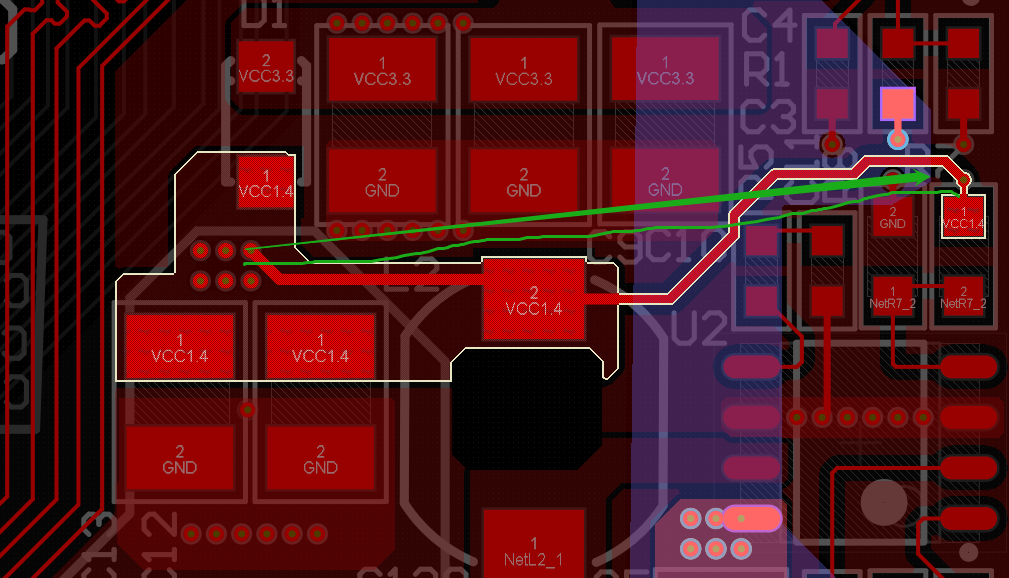

反馈要从电容后面取样2.注意过孔不要上焊盘3.走线尽量不要从电阻电容中间穿4.丝印调整不到位,注意丝印不要上焊盘5.顶层BGA里面的铜尽量挖掉6.此处走5mil地线太细,建议最少12mil以上以上评审报告来源于凡亿教育90天高速PCB特训班

本视频主要讲解关于我们如何修改我们的对应的封装丝印等的属性和字体,同时讲了关于我们原理图为什么修改不成功和PCB为什么能够修改成功,以及我们的操作的注意的事项的一个讲解。

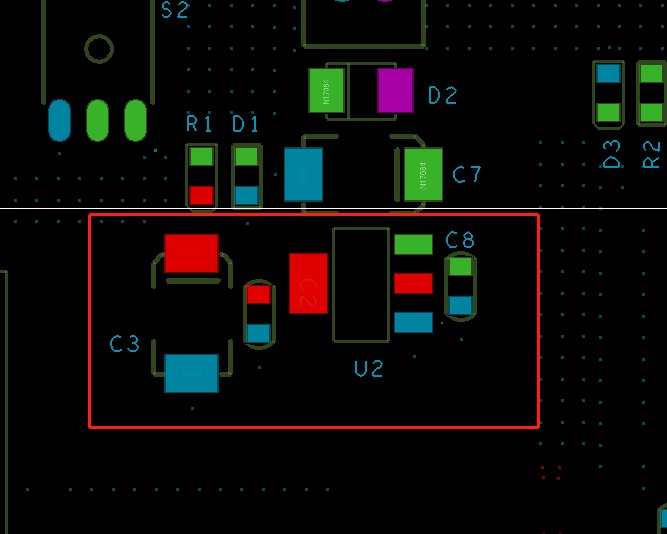

注意下器件整体对齐:器件位号不要覆盖再焊盘上,设计完成之后都是需要调整器件丝印:晶振需要就近靠近IC对应管脚放置:走线注意规范,不要从电容内部走线,更换下路径:建议看下此处VBAT 20MIL是否满足载流:上述一致问题,从电阻内部走线:以上

扫码关注

扫码关注