- 全部

- 默认排序

ESD保护原理及选型

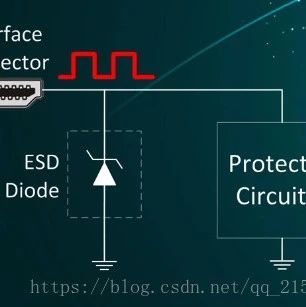

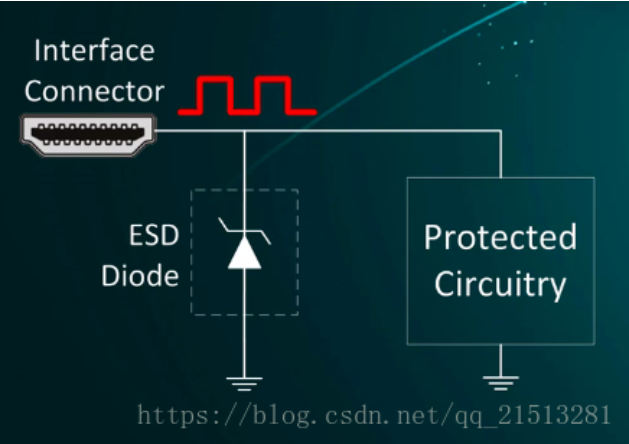

通常情况ESD保护电路如下当系统没有干扰,正常工作时,ESD器件可以忽略,几乎不起作用当外部接口电压超过ESD器件的击穿电压(VBR),ESD器件开始起作用,并将电流分流到地。实际ESD器件的工作电压(VRWM)与击穿电压(VBR)的区别,选择ESD器件应该选择系统工作电压小于ESD器件的工作电压(

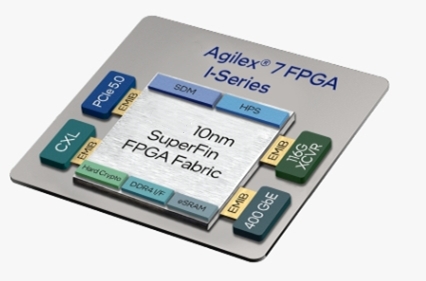

说明Agilex™ 7 FPGA 和 SoC FPGA I 系列产品面向带宽密集型应用,采用英特尔 10 纳米 SuperFin 制程技术打造而成,在 F 系列设备功能的基础上进行了扩展,可提供高达 116 Gbps 的收发器速率、支持 P

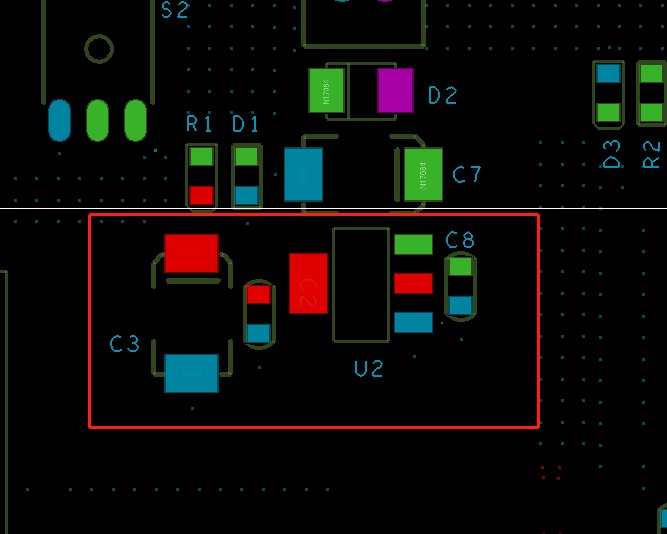

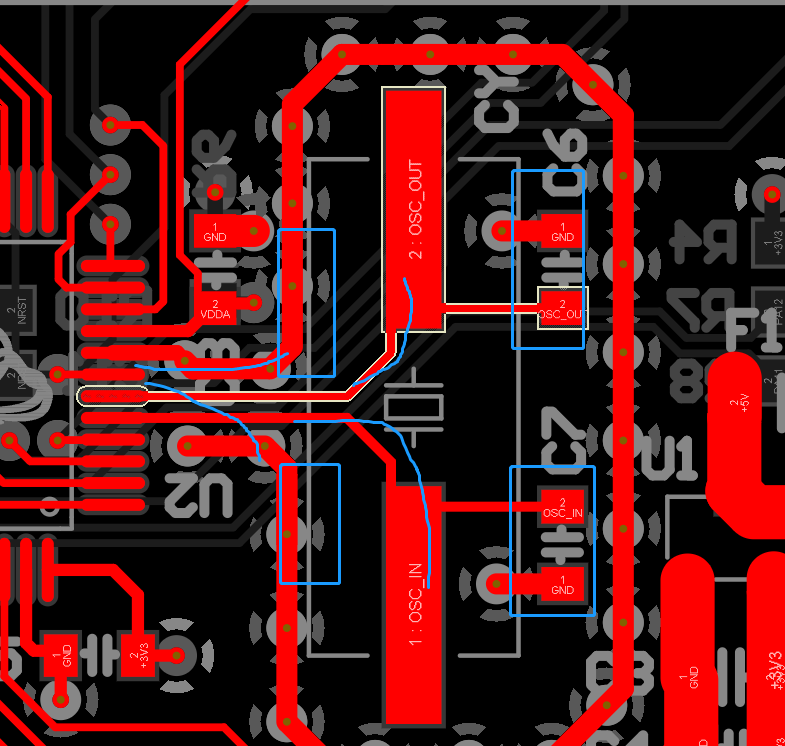

注意下器件整体对齐:器件位号不要覆盖再焊盘上,设计完成之后都是需要调整器件丝印:晶振需要就近靠近IC对应管脚放置:走线注意规范,不要从电容内部走线,更换下路径:建议看下此处VBAT 20MIL是否满足载流:上述一致问题,从电阻内部走线:以上

一、名词解析(1)VCC:C=circuit 表示电路的意思, 即接入电路的电压(2)VDD:D=device 表示器件的意思, 即器件内部的工作电压;(3)VSS:S=series 表示公共连接的意思,通常指电路公共接地端电压(4)VEE

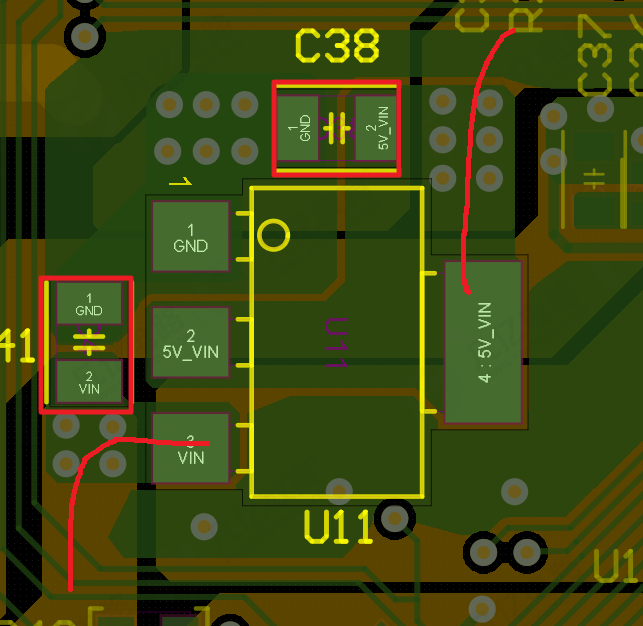

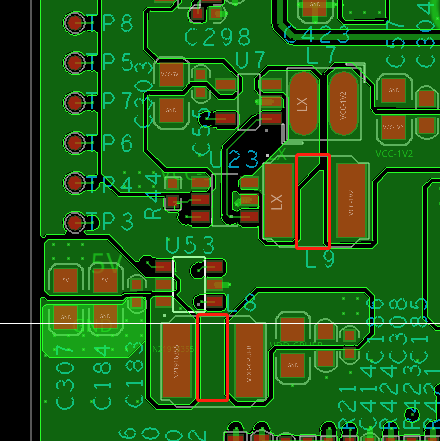

1.电流没有经过电容,过孔应该打在电容后面。2.器件摆放太近,应避免造成丝印干涉3.过孔应打在第一个电容,信号经过第一个电容到第二个电容。4.应按原理图顺序摆放器件,过孔打在第一个器件前方。5.VBAT的滤波电容靠近管脚放置6.滤波电容尽量

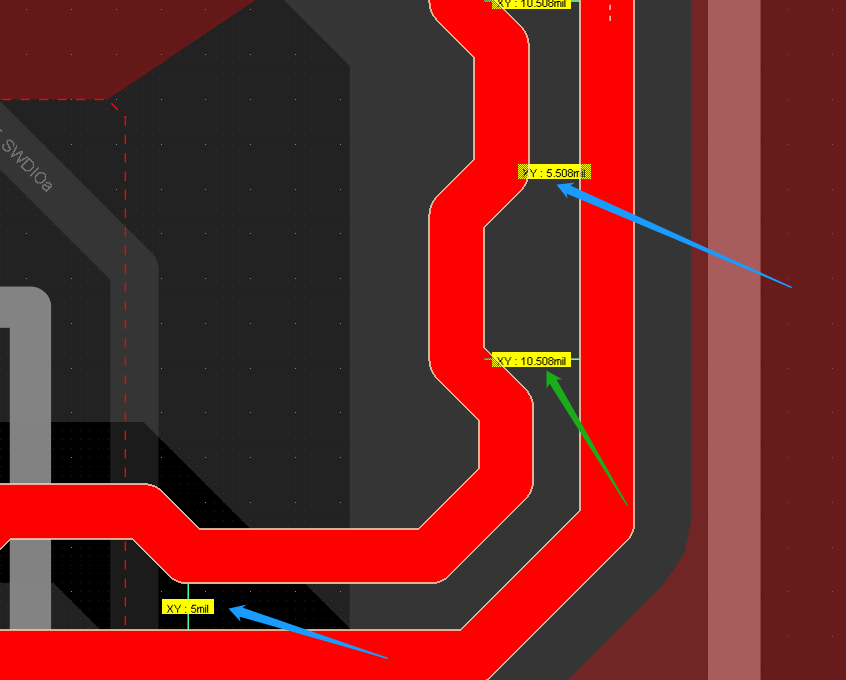

差分走线不满足差分间距要求,锯齿状等长也不能超过线距的两倍2.滤波电容和EAD器件靠近管脚放置3.输出打孔要打在最后一个滤波电容的后面4.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.此处走线不满足载流6.VBAT的滤

晶振布局需要调整2.焊盘出线不规范3.USB这对差分走线需要耦合,对内等长误差5mil4.没有添加USB控90的class,创建差分对5.VBut属于电源信号,走线需要加粗6.此处不满足载流以上评审报告来源于凡亿教育邮件公益作业评审如需了解

带你干所在层的内部需要挖空处理2.天线做隔层参考,需要挖空第二层3.差分对内等长处理不当,锯齿状凸起高度不能超过线距的两倍4.晶振需要走内差分,并包地,多打地过孔5.注意数据线等长需要满足3W规则6.地址线也需要满足3W规则7.网口差分需要

通常情况ESD保护电路如下当系统没有干扰,正常工作时,ESD器件可以忽略,几乎不起作用当外部接口电压超过ESD器件的击穿电压(VBR),ESD器件开始起作用,并将电流分流到地。实际ESD器件的工作电压(VRWM)与击穿电压(VBR)的区别,

通常情况ESD保护电路如下当系统没有干扰,正常工作时,ESD器件可以忽略,几乎不起作用当外部接口电压超过ESD器件的击穿电压(VBR),ESD器件开始起作用,并将电流分流到地。实际ESD器件的工作电压(VRWM)与击穿电压(VBR)的区别,

扫码关注

扫码关注