- 全部

- 默认排序

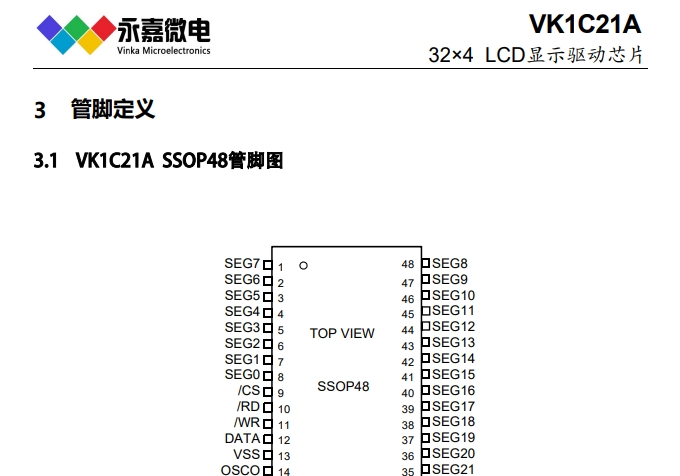

VK1C21A是一个点阵式存储映射的LCD驱动器,可支持最大128点(32SEGx4COM)的LCD屏,也支持2COM和3COM的LCD屏。单片机可通过3/4个通信脚配置显示参数和发送显示数据,也可通过指令进入省电模式。具备高抗干扰,显示效

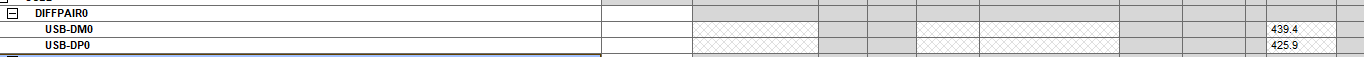

注意器件摆放不要干涉,贴片器件尽量离座子1.5mm2.走线需要优化一下3.差分走线不满足间距要求4.打孔要打在ESD器件前面5.器件摆放尽量中心对齐处理,更美观6.差分锯齿状等长不能超过线距的两倍7.注意差分出线要尽量耦合8.USB差分对内

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

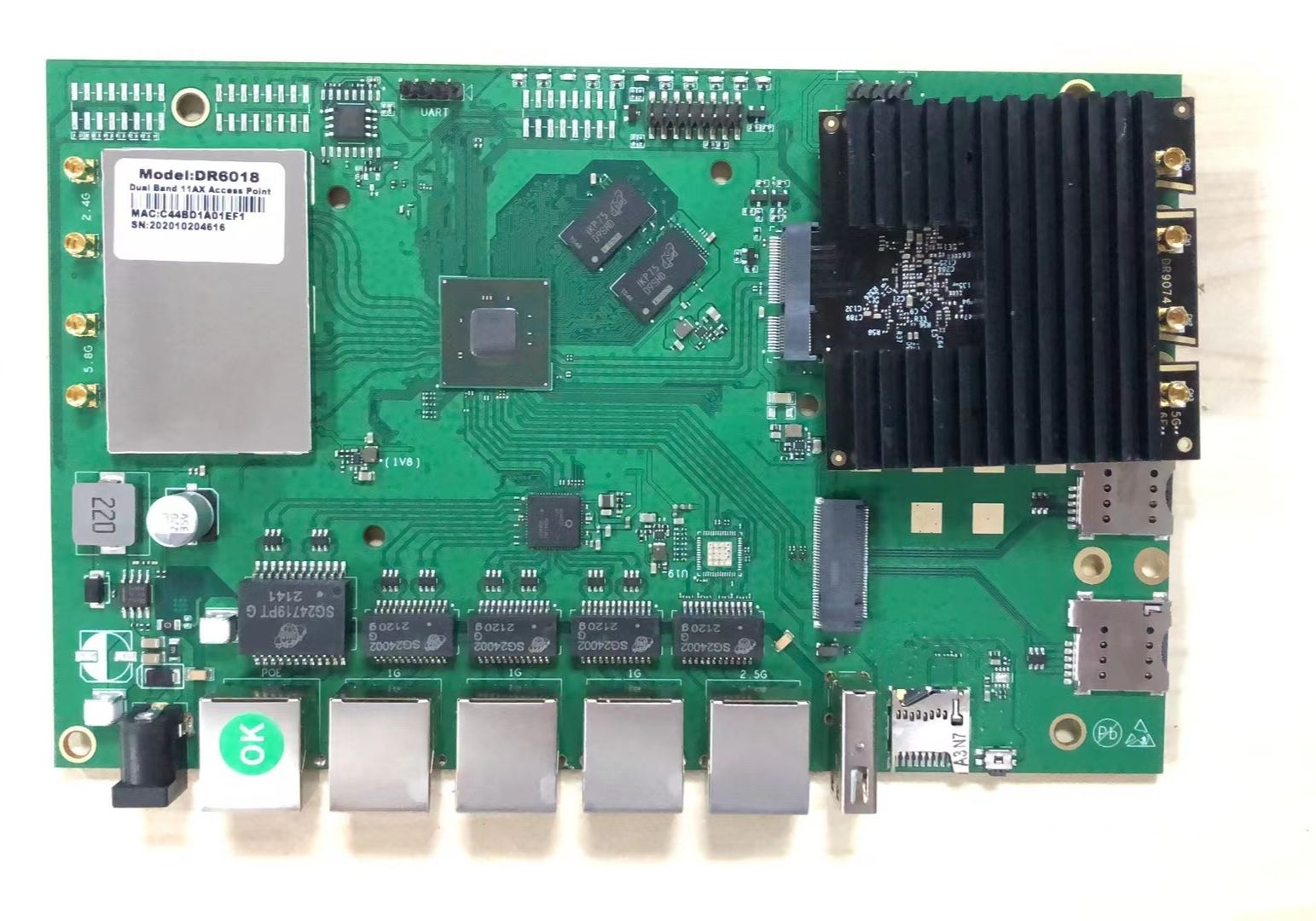

QSDK QCN9074/QCN9024/QCN6024 wifi6 card 802.11ax 4x4 MU-MIMO 6GHz wifi6E M.2Features■ Qualcomm AtherosQCN9074■ 6GHz, max

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

ADM2582E/ADM2587E是具备±15 kV ESD保护功能的完全集成式隔离数据收发器,适合用于多点传输线路上的高速通信应用。其内部集成的RS-485驱动器带有一个高电平有效使能电路。

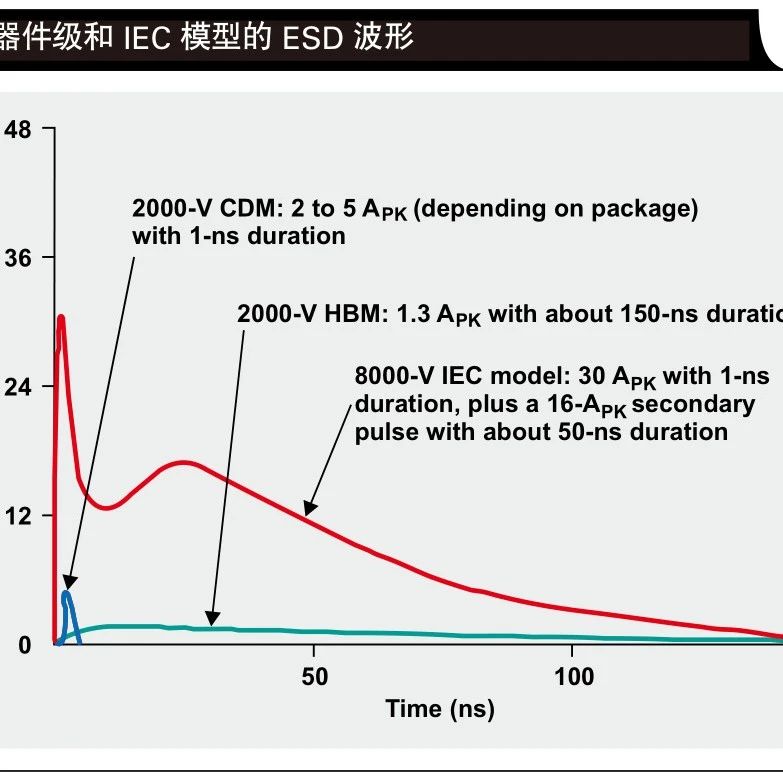

系统级ESD设计考虑

1、引言随着技术的发展,移动电子设备已成为我们生活和文化的重要组成部分。平板电脑和智能手机触摸技术的应用,让我们能够与这些设备进行更多的互动。它构成了一个完整的静电放电 (ESD) 危险环境,即人体皮肤对设备产生的静电放电。例如,在使用消费类电子设备时,在用户手指和平板电脑 USB 或者 HDMI

差分对内等长误差器件顺序不对应该先经过eSD在经过电阻USB3.0:差分包地每组都要包地的地线上要打回流地过孔差分对内没有做等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:ht

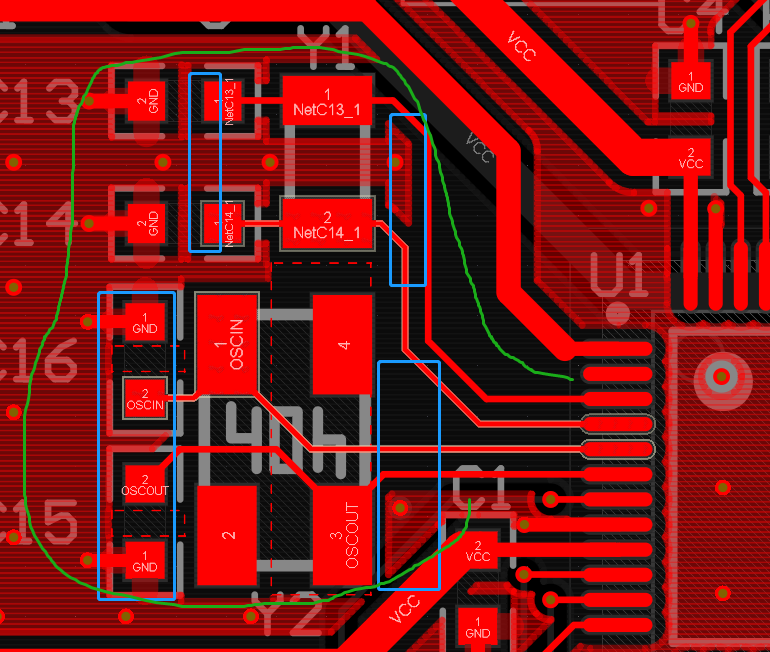

晶振布局处理不当,电容应该靠近芯片放置,并包地处理2.SD卡需要进行整组包地处理3.出线尽量从焊盘中间出线,此处可以在优化一下4.此处过孔尽量打在走线上或者直接删掉即可5.pcb上存在无网络过孔以上评审报告来源于凡亿教育90天高速PCB特训

扫码关注

扫码关注