- 全部

- 默认排序

01—为何要测关断功率Transmit OFF power 定义为发射机关断时的信道带宽内的平均功率,而且至少一个子帧(1ms)持续时间内的平均功率。那么什么是发射机的关断状态呢?有以下情形:是指终端不被允许发射期;或不发射sub-fRAM

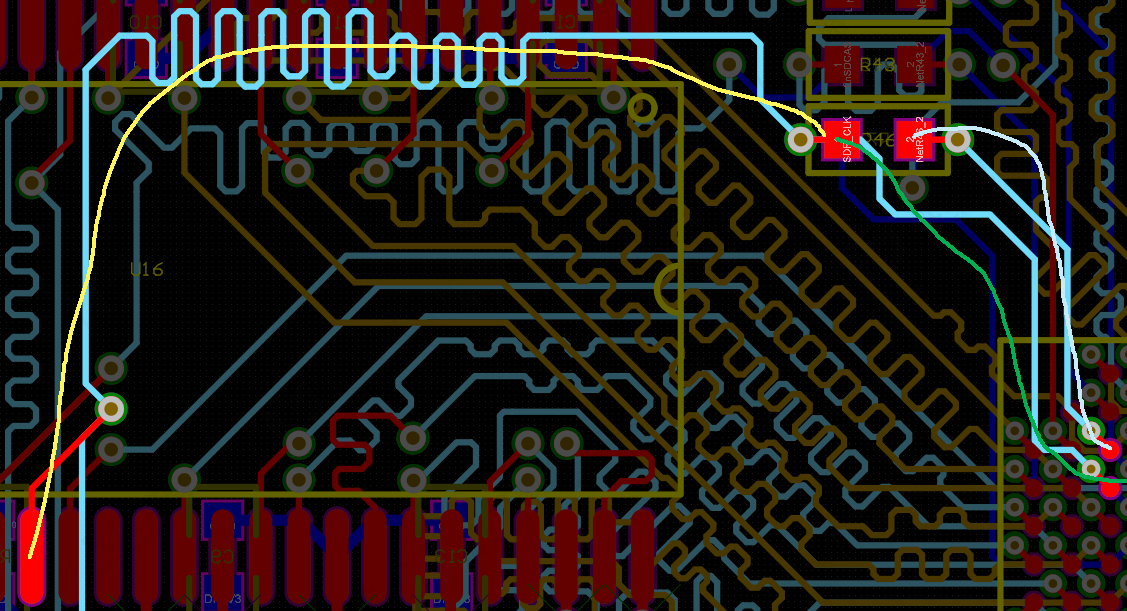

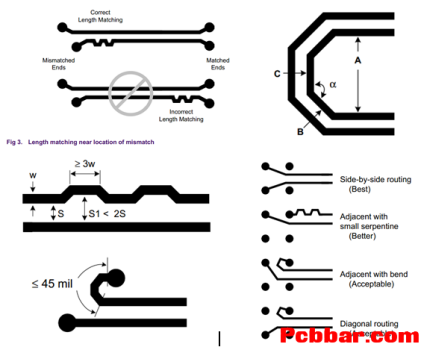

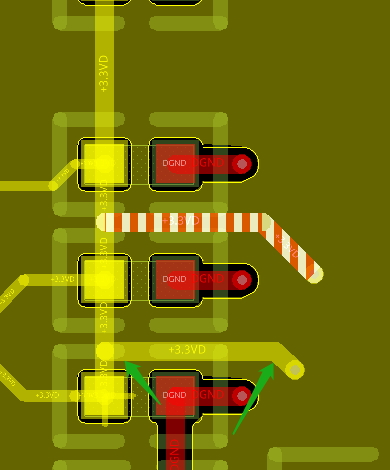

时钟信号等长错误数据线分组却少网络等长绕线太丑,信号流向尽量顺畅以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

为啥单片机RAM那么少?

你肯定好奇:手机内存(RAM)动辄8G、12G,为啥单片机RAM连1M都不到?经典的AT89C51单片机,其内部只有128字节RAM(内存),同样经典的MSP430F149也只有2K的RAM空间。即使现在用的比较多的STM32F1系列,其最

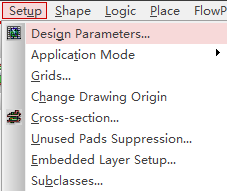

答:我们使用Allegro软件进行设计PCB图纸之前,需要对整个设计的参数进行设置,需要执行菜单命令Setup-Design PaRAMeters,如图5-50所示:

器件尽量整体中心对齐:等长线的gap大于等于3W:地址数据等长误差没什么问题 ,都在误差范围内:其他的基本没什么问题,完成得还可以。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:

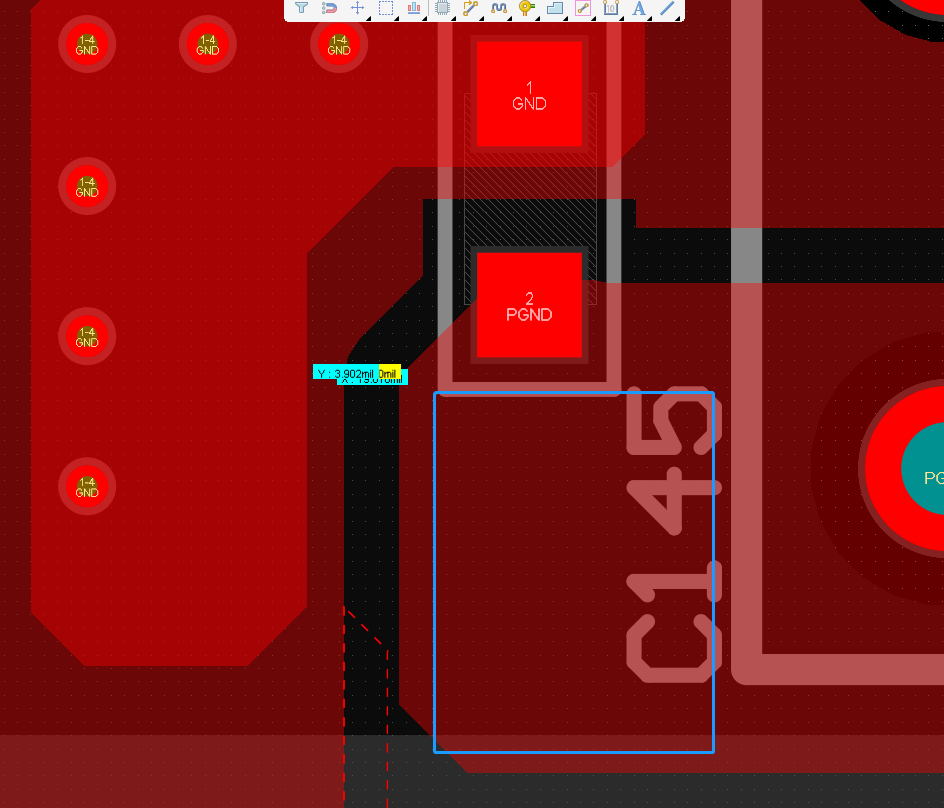

跨接电容旁边进行多打地过孔,不同的地间距建议2mm2.器件干涉3.SDRAM等长还存在没有达到目标值4.走线尽量不要从电阻电容中间穿5.滤波电容应该靠近输入管脚放置以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

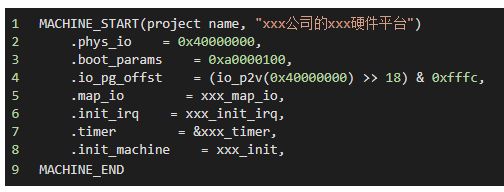

作为一个多年耕耘在linux 2.6.23内核的开发者,各个不同项目中各种不同周边外设驱动的开发以及各种琐碎的、扯皮的俗务占据了大部分的时间。当有机会下载3.14的内核并准备学习的时候,突然发现linux kernel对于我似乎变得非常的陌生了,各种新的机制,各种fRAMework、各种新的概念让我感到阅读内核代码变得举步维艰。还好,剖析内核的热情还在,剩下的就交给时间。

扫码关注

扫码关注