- 全部

- 默认排序

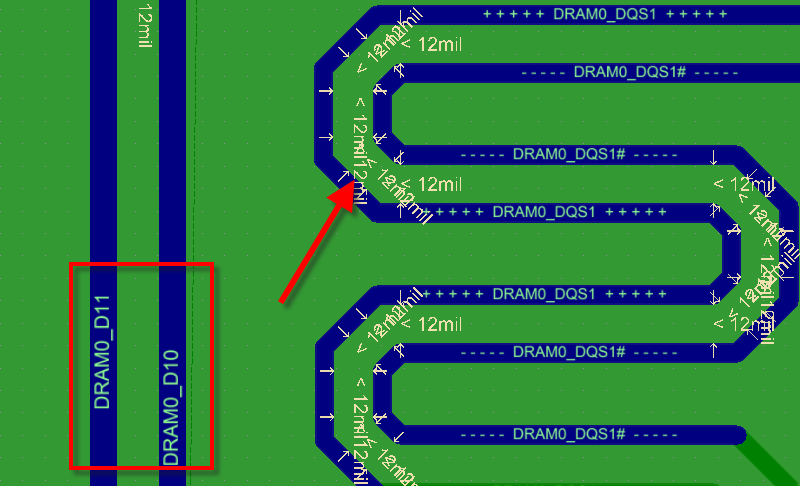

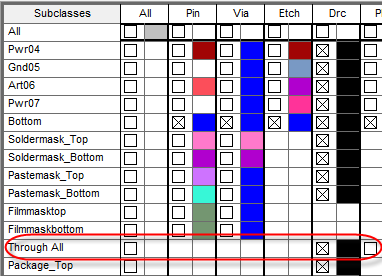

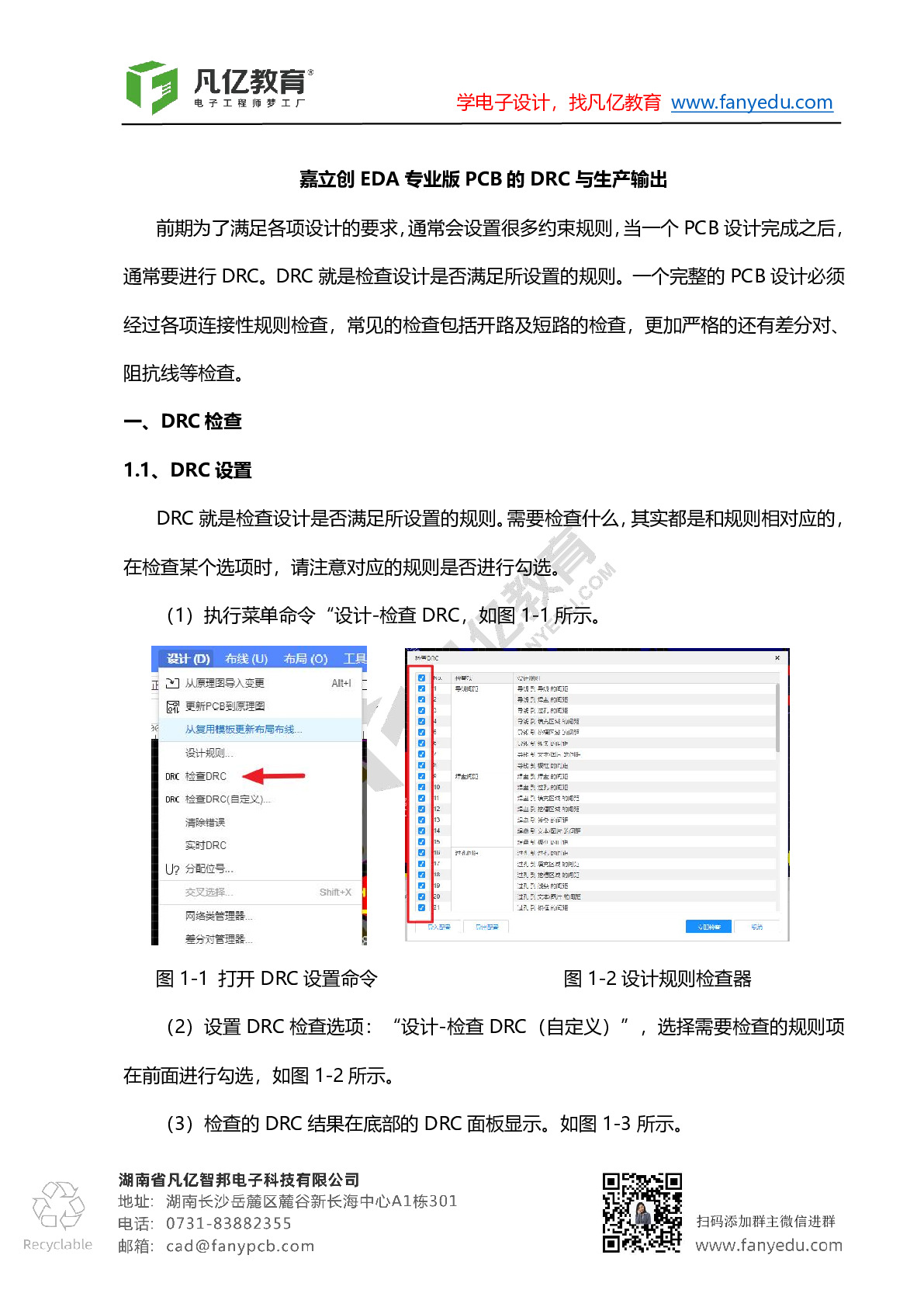

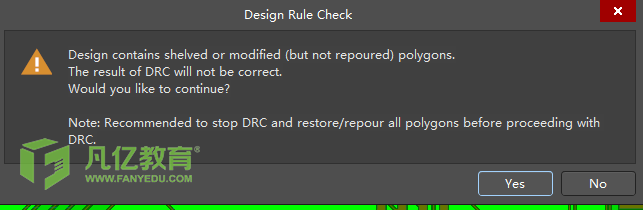

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

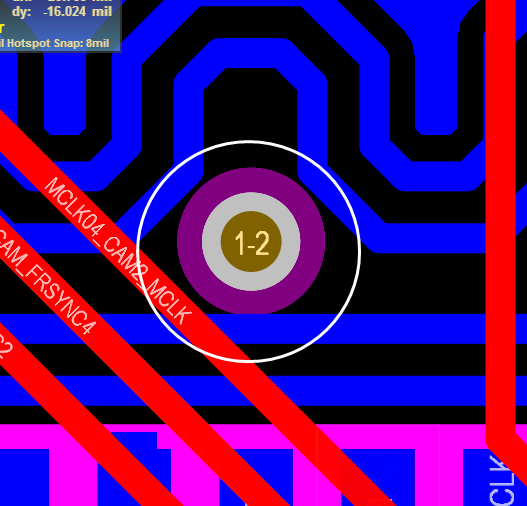

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

DRC问题

报错内容如下:Polygon named: Bottom Layer-No Net In net GND On 01Top Layer但是AD9却不会报此类错误,请教各位大佬这是怎么回事。

扫码关注

扫码关注