- 全部

- 默认排序

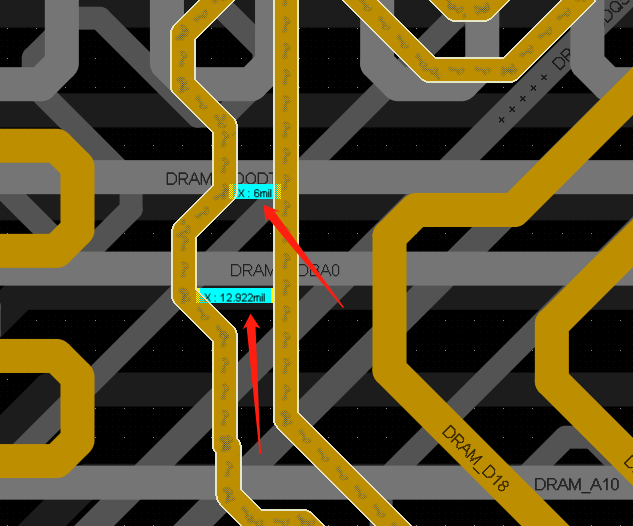

差分线对内等长凸起高度不能超过线距的两倍2.等长线之间尽量要满足3W规则,后期自己调整一下走线间距3.电源走线路径要尽量短,后期自己优化一下走线路径4.左右声道尽量单根包地5.差分走线要尽量耦合出线,后期自己调整一下地过孔6.注意天线部分挖

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。

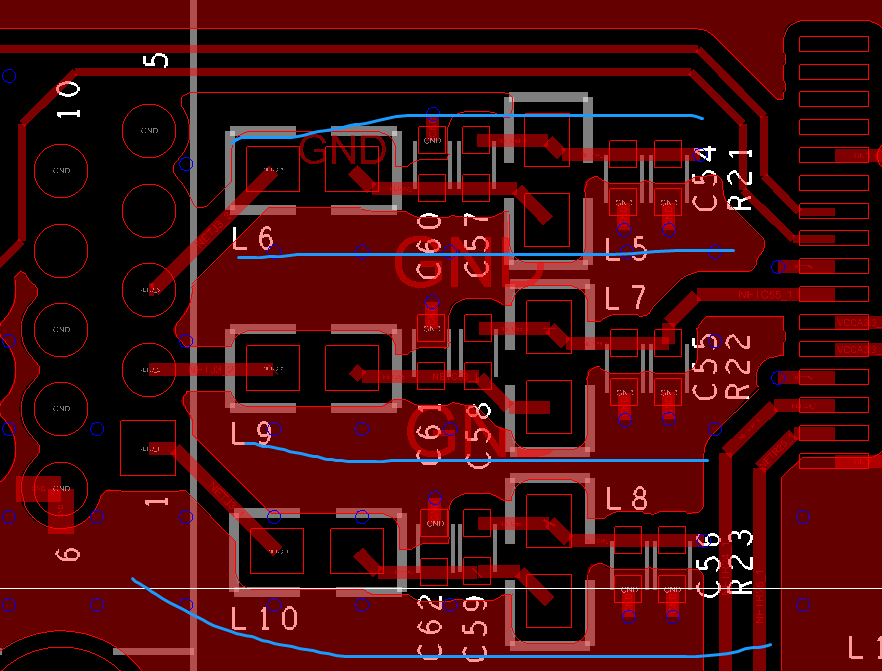

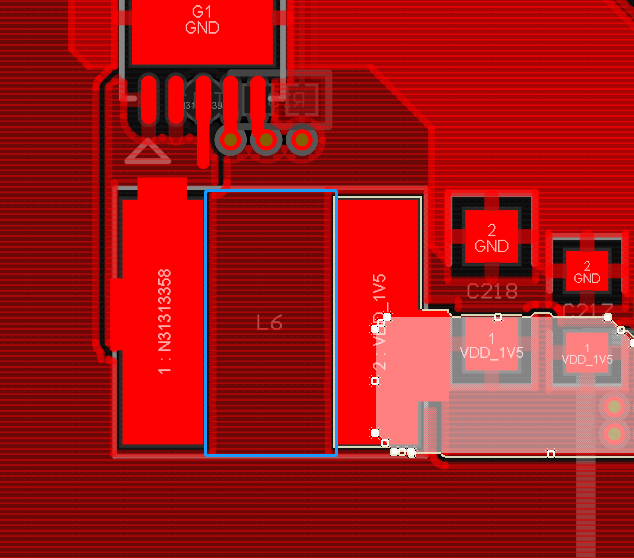

模拟信号尽量一字型布局,并单根包地2.锯齿状等长不能超过线距的2倍3.网口除差分信号外,其他都需要加粗到20mil4.电感所在层的内部需要挖空处理5.反馈路劲需要从电容后面取样6.注意数据线直接拿等长需要满足3W规则7.地址线之间也需要满足

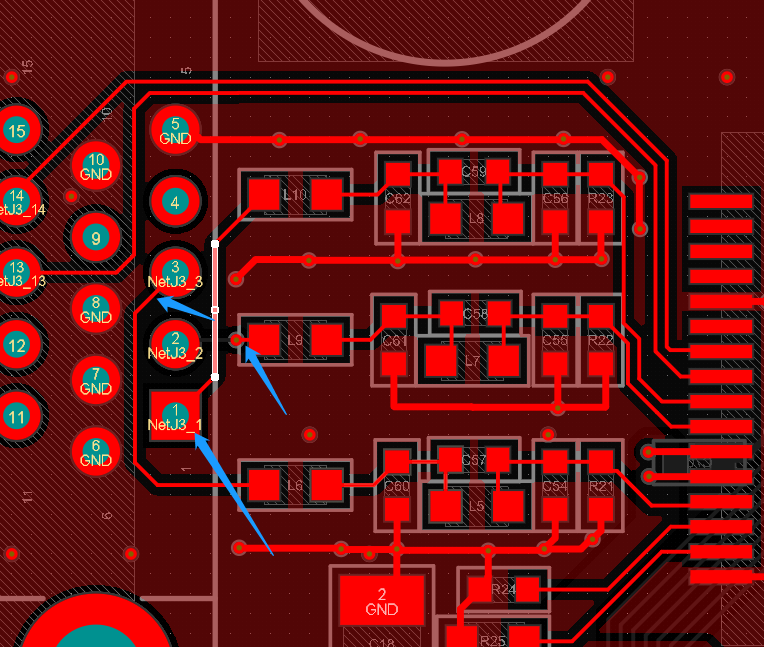

差分线处理不当,锯齿状等长不能超过线距的两倍2.注意地址线之间等长需要,满足3W规则3.差分对内等长不满足误差范围4.走线未连接到过孔中心,存在开路5.滤波电容法放置尽量保证一个管脚一个6.此处不满足载流,建议铺铜处理7.数据线之间等长也需

VGA的模拟信号需要加粗2.数据线等长需要满足3W规则3.地址线也需要满足3W规则4.挖空电感所在层即可5.变压器除差分之外其他的信号都需要加粗20mil6.外壳地和GND的间距最少需要20mil7.网口差分需要进行对等长,误差为5mil8

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于

电感所在层的呢恩不需要挖空2.差分线对内等长处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.注意数据线等长需要满足3W规则4.差分出线要尽量耦合5.存在多余的线头6.注意过孔不要上焊盘7.注意器件摆放过近,建议最少1.5mm8.过孔需要

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★掌握DDR的设计方法★掌握蛇形等长走线,掌握3W规则的应用★了解常见EMC的PCB处理方法。

器件摆放太近,建议2mm2.晶振尽量靠近芯片摆放,走内差分,并包地处理3.注意TX,RX等长线之间需要满足3W规则4.TX整组包地少一根TXD35.电源信号可以在电源层处理6.此处差分走线需要优化一下7.变压器除产信号外,其他的都需要加粗到

扫码关注

扫码关注