- 全部

- 默认排序

最近硬件工程师同行提出疑问,在硬件设计过程中layout完成后有DRC检查,已经对设计工艺规则做了检查,那么DFM可制造性分析还有必要吗?今天就为大家用一篇文章说明下DRC与DFM两者的区别。可制造性设计 (DFM) 是一种设计验证方法,与

Orphaned copper starting from : Region (0 hole(s)) Top Layer老师,这个错误是什么意思??Net +3.3V is broken into 1 sub-nets. Routed To 100.00% Subnet : R148-2 R150-

PCB 进行design rule check 时报错,提示Un-Routed Net Constraint: Net V_VS Between Track (33.223mm,-13.425mm)(34.781mm,-13.425mm) on Bottom Layer And Pad R85-2(

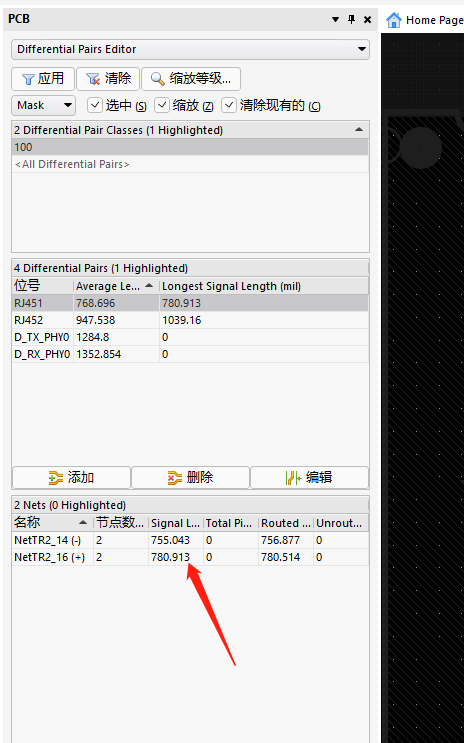

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处DRC7.时钟信号包地,尽量

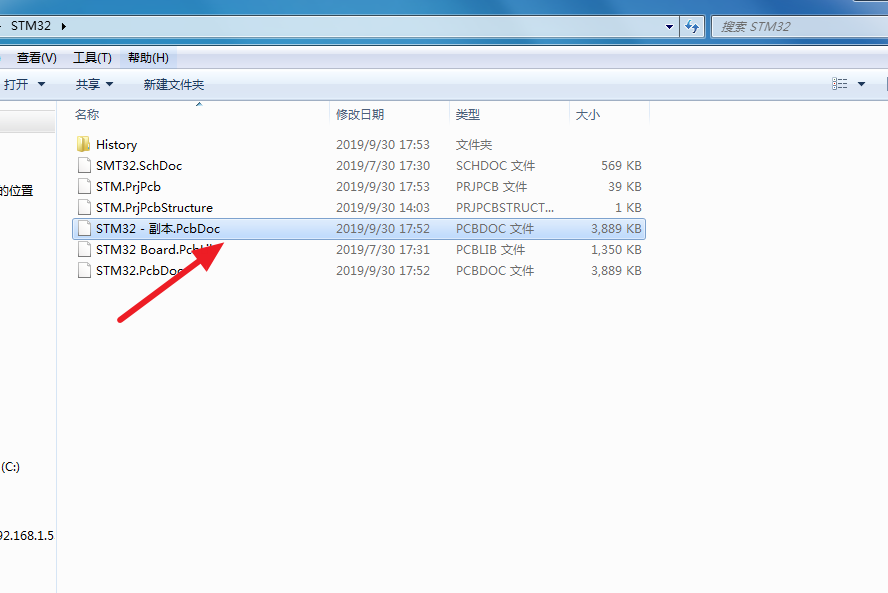

PCB设计在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,以为已经连接到了焊盘中心点上,其实没有。那么,这个对于我们后期会造成虚焊,并且这一项有时DRC也检查不出来。所以为了减少我们不必要的损失,就需要去进行检查。2.走线跟走线连接的时候,本以为是连接上了,但是没有连接上来,会有开路的现象。

安全间距DRC检查

安全间距DRC检查主要是检查各元素间设计的距离是否小于规则内设置的距离,若小于则会有短路风险,通过DRC检查可以将报错的位置显示出来,方便设计师进行DRC消除。进行安全间距DRC检查前,建议大家先把铜皮处理好,把所有电气层打开,将PCB整板

扫码关注

扫码关注