- 全部

- 默认排序

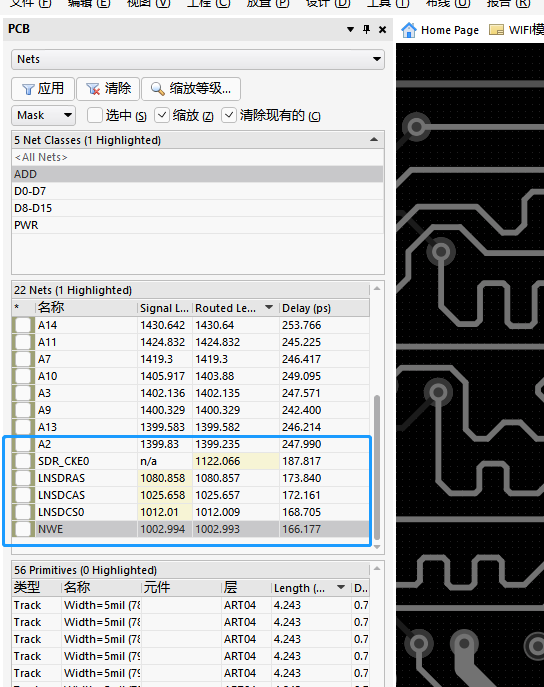

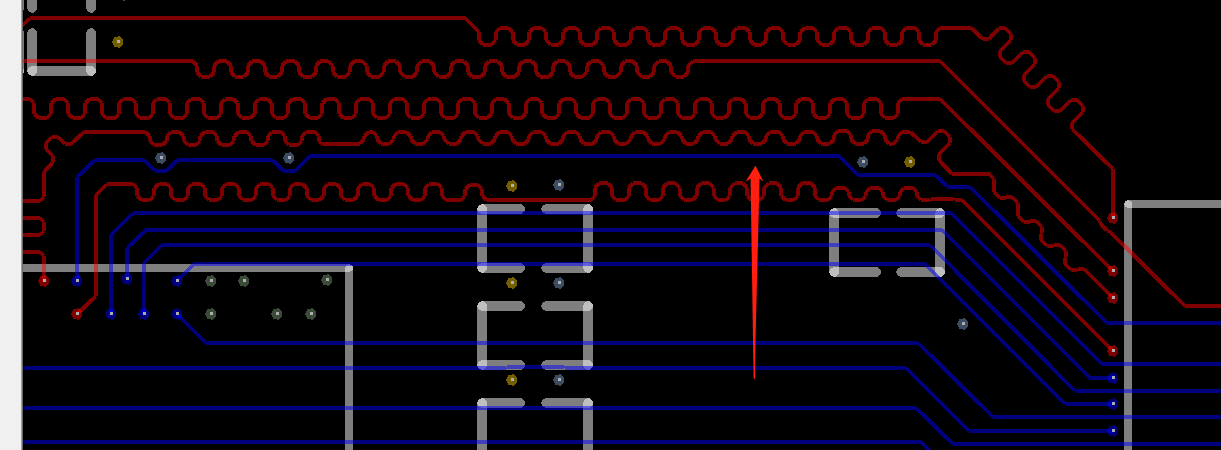

等长存在报错,电阻另一端需要看成一根进行等长2.此处一层连通无需打孔3.滤波电容尽量靠近管脚放置4.过孔需要盖油处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

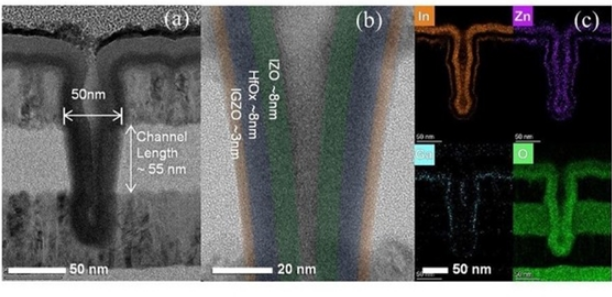

近日,日本媒体报道,声称华为将在2022年超大规模集成电路研讨会(VLSI Symposium)期间发布新型3D DRAM技术,并进行各种有关内存的演示,该技术是与中科院微电子研究所合作开发的。据媒体内容,华为将要发布的3D DRAM技术,

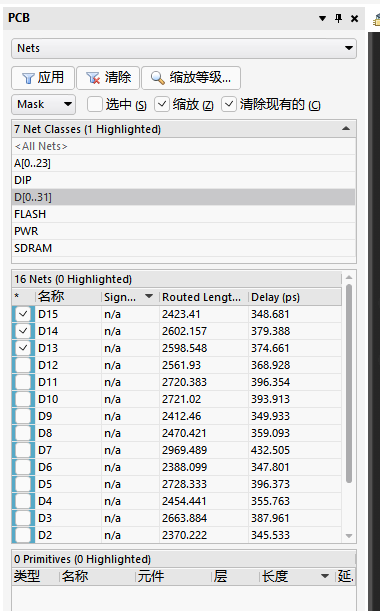

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

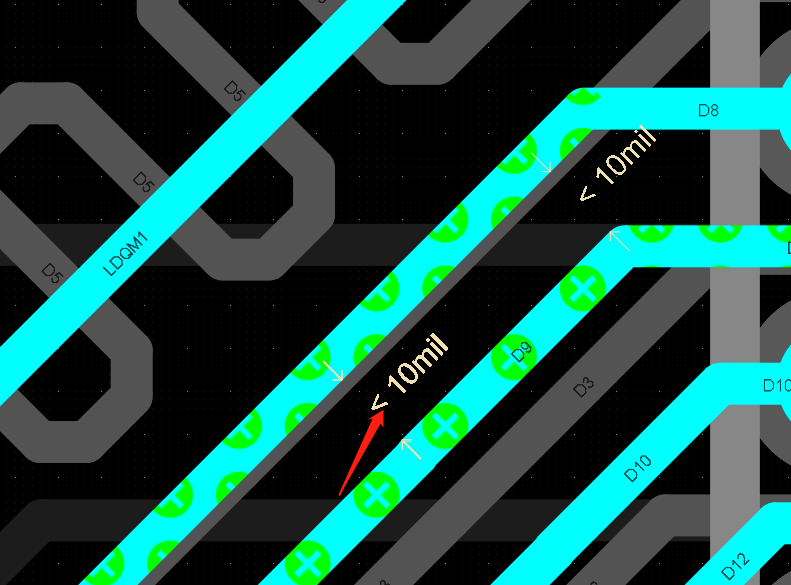

注意数据线之间等长需要满足3W2.次根信号等长不满足原理图要求3..地址线之间等长也需要满足3W4.存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

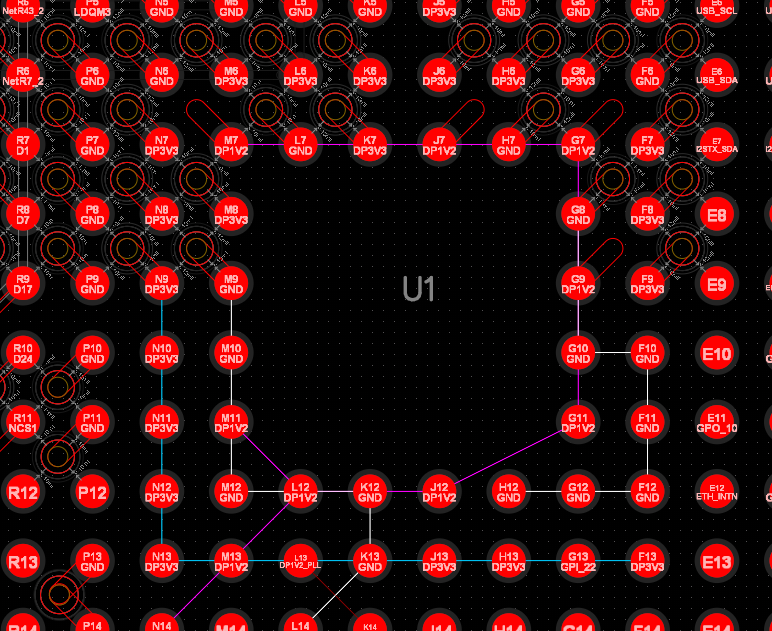

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

我是2018年09月18号加入凡亿弟子计划跟着郑老师学习AD画板子的。郑老师在和我通过电话,了解了基本情况以后,制定了学习计划。从最基本的电源模块入手开始学习如何画板,通过这两个月的学习,现在已经能把SDRAM画好了,这里说说这两个月来的感受。

注意数据线和地址线之间需要满足20mil的间距要求2.存在短路3.注意数据线和地址线需要进行等长处理,并满足3W间距4.走线注意能拉直尽量拉直5.扇孔可以在优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

注意数据线之间等长需要满足3W2.串组两端的信号也要加入地址信号进行等长3.地址线和数据线之间需要画一根地线进行分开4.电源需要再电源平面层进行处理,打孔进行连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

回答网友的问题:逻辑电路设计规则里gate width方向的尺寸一般要求远比feature size大,比如28nm的gate width最小也是100nm,间隔也最小80nm,这是出于什么考虑呢?有没有可能跟DRAM工艺那样,也压到fea

扫码关注

扫码关注