- 全部

- 默认排序

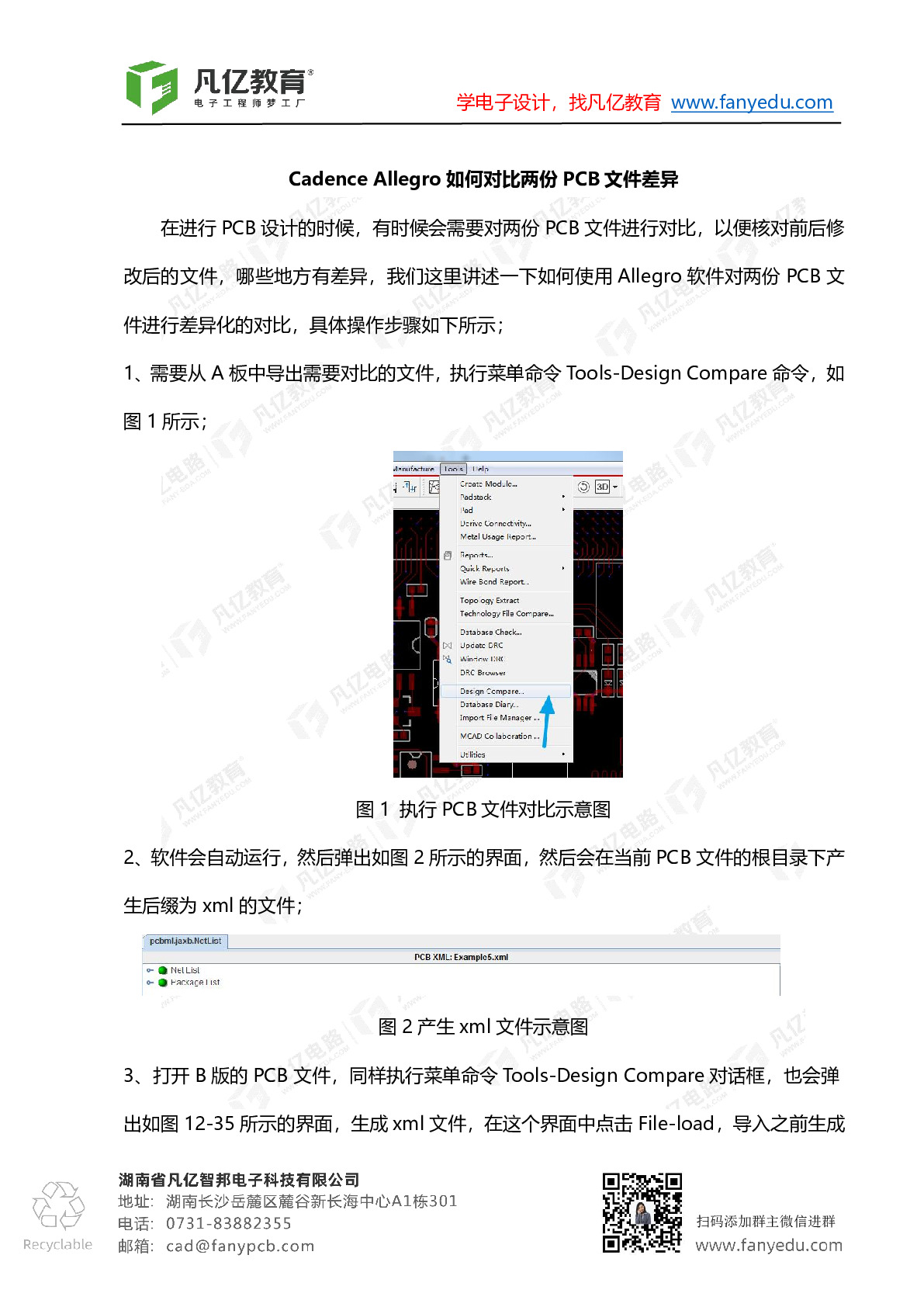

小白初入PCB设计领域,最先接触到的EDA软件必然是Altium Designer、PADS和Cadence,而其中的Altium Designer因操作容易易懂,受众广特点成为首选PCB设计软件,今天我们将分享关于四个Altium Des

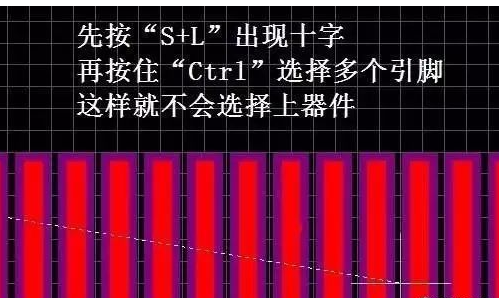

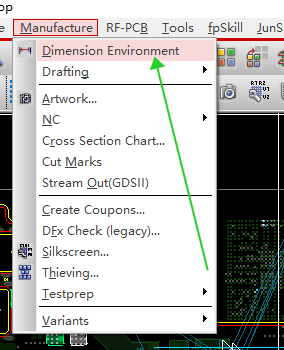

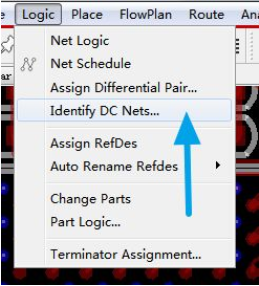

Cadence Allegro飞线的隐藏关闭在PCB设计过程中,一把布线的顺序是先走信号线,然后进行电源的处理、电源的分割,然而电源的飞线是非常多的,非常影响信号线的布线,所以刚开始会将电源的飞线进行隐藏,具体操作的步骤如下所示:1. 点击

使用凡亿Skill脚本的Layout---Align Objects命令,自动对齐工具,可对齐丝印,器件,过孔。出现了以下错误,怎么解决, Cadence版本17.4Failed to open form align.form. *Error* axlFormSetField: argument #1 should be any user-defined (other) type (type template = "otg") - nil

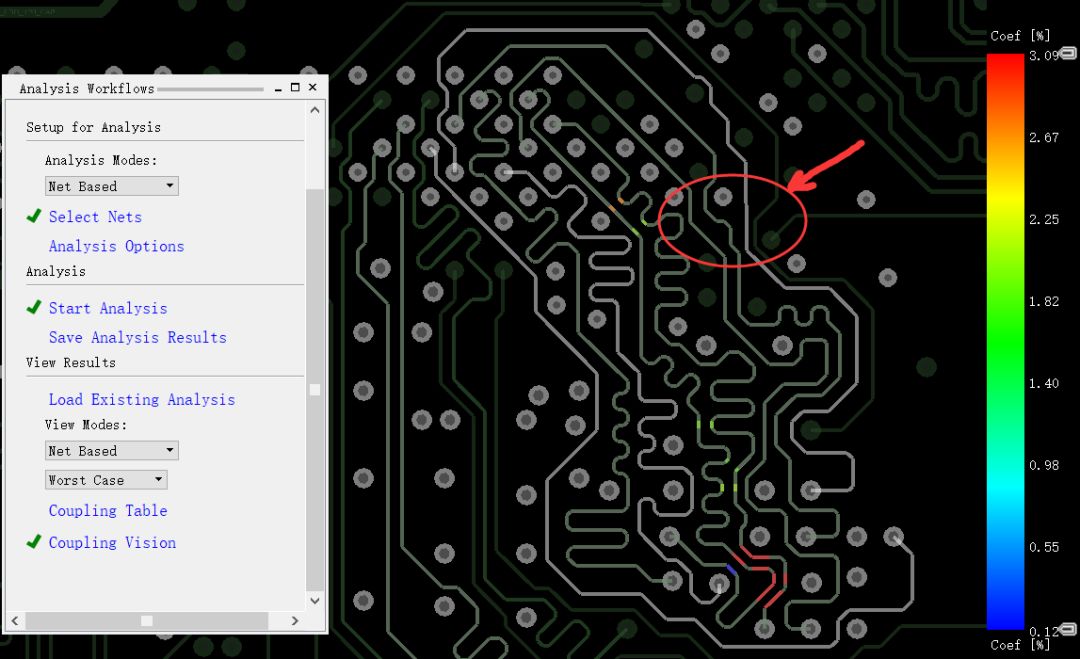

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

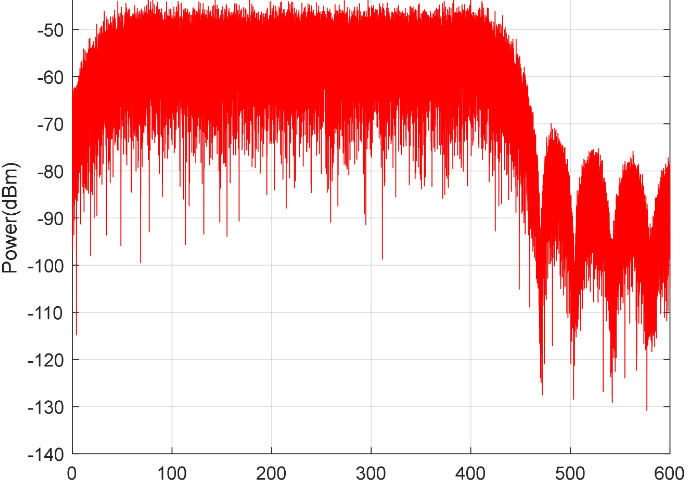

MATLAB是电子工程师的基础技能之一,学习MATLAB也有利于为就业转职增加筹码。今天将分享关于MATLAB的高级机器啊,如何在MATLAB中绘制信号的频谱图?横坐标如何标注出频率值?绘制过程中需要注意什么?学习Cadence Sigri

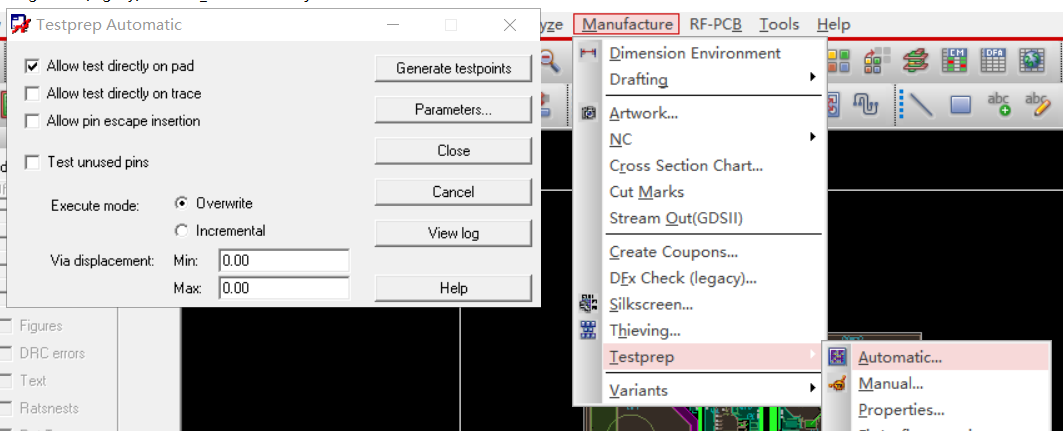

Cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

扫码关注

扫码关注